# Universidad de Alcalá Escuela Politécnica Superior

## DEPARTAMENTO DE ELECTRÓNICA

# GRADO EN INGENIERÍA EN TECNOLOGÍAS DE LA TELECOMUNICACIÓN GRADO EN INGENIERÍA EN SISTEMAS DE TELECOMUNICACIÓN GRADO EN INGENIERÍA EN ELECTRÓNICA DE COMUNICACIONES GRADO EN INGENIERÍA EN TELEMÁTICA

| ASIGNATURA | ELECTRÓNICA DIGITAL (1ª parte) | Fесна       | 1-6-2011 |

|------------|--------------------------------|-------------|----------|

| APELLIDOS  |                                | DNI         |          |

| Nombre     |                                | Grupo       |          |

| TITULACIÓN |                                | Nº DE LISTA |          |

| 1 | 2 | 3 | 4 |   | Т |

|---|---|---|---|---|---|

|   |   |   |   | = |   |

#### NORMATIVA DEL EXAMEN

- En primer lugar, escriba su nombre y apellidos en el espacio reservado a tal efecto y deje un carné de identidad o de la escuela visible a su lado.

- **Apague** su teléfono móvil.

- Esta parte tiene un valor de **4 puntos**, y es obligatoria para todos los alumnos. Tiene una duración de **dos horas**.

- Las respuestas que no estén **claramente justificadas** y razonadas **no tendrán ningún** valor.

- El uso de cualquier documentación auxiliar y del teléfono **móvil** está completamente **prohibido**.

- **Conteste** a las preguntas en el espacio disponible **en estas hojas**. No se corregirán hojas entregadas aparte.

- La cuestión relativa al **laboratorio** es la **cuestión 4**. Aquellos alumnos que tengan convalidado el laboratorio deben indicarlo en esta cuestión escribiendo únicamente en el espacio reservado a la solución: "Laboratorio convalidado".

#### Cuestión 1 (10 puntos)

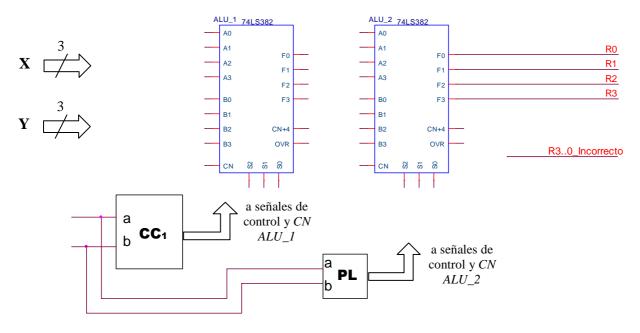

El esquema de la figura 1.1 está pensado para operar con dos números X e Y de 3 bits codificados en C2, realizando la operación R=|X| más |Y|. La operación es efectuada por 2 ALU's Y el resultado se obtiene en 4 bits en R ( $R_3$ .. $R_0$ ), interpretado también en X está bloque X está un bloque combinacional con 2 entradas (X está penera las señales de control de X está X está penera las señales de control de X está X e

*NOTAS*:(1) El cometido de  $ALU_2$  es resolver la situación en que X e Y son ambos negativos, en el resto de casos no altera el resultado de  $ALU_1$ . (2) tenga en cuenta que -x-y=-(x+y).

Figura 1.1

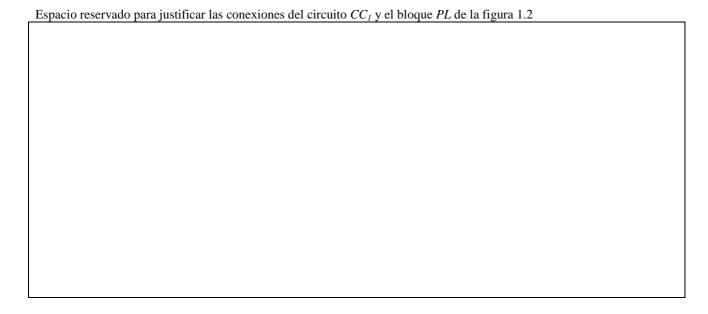

1) Complete la tabla mostrada a continuación con las operaciones que debe realizar el circuito para operar con X e Y de la manera descrita. Indique en cada caso el intervalo de posibles valores que se pueden dar, y si puede haber desbordamiento, en  $R_3$ .  $R_0$ . Complete además todas las conexiones del circuito de la figura 1.2 sin incluir ningún componente adicional. (7 ptos.)

NOTA: El circuito  $CC_1$  está diseñado con un multiplexor y una única puerta lógica de 2 entradas y el bloque PL contiene dos puertas lógicas de 2 entradas

| X        | Y        | Operación que debe<br>realizar el circuito<br>completo sobre X e Y. | Operación que<br>realiza ALU_1 | Operación que<br>realiza ALU_2 | Intervalo de valores en R <sub>3</sub> R <sub>0</sub> | Posible<br>desbordamiento en<br>R <sub>3</sub> R <sub>0</sub> ? (Sí/NO) |

|----------|----------|---------------------------------------------------------------------|--------------------------------|--------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------|

| Positivo | Positivo |                                                                     |                                |                                |                                                       |                                                                         |

| Positivo | Negativo | X menos Y                                                           | A menos B                      |                                |                                                       |                                                                         |

| Negativo | Positivo |                                                                     |                                |                                |                                                       |                                                                         |

| Negativo | Negativo |                                                                     |                                |                                |                                                       |                                                                         |

Figura 1.2

2) Obtenga, en la circuito de la figura 1.2, la señal  $R_{3..0}$ \_Incorrecto sin añadir ningún componente adicional. Proponga, en la misma figura y sin añadir ningún componente adicional, una ampliación a un 5° bit de resultado,  $R_4$ , que corrija R en caso de ser incorrecto. (3 ptos.)

#### Cuestión 2 (10 puntos)

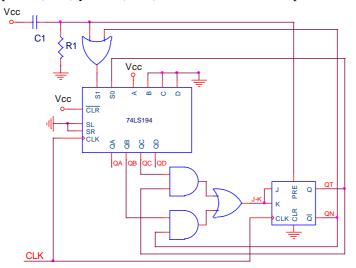

En la figura 2.1 se muestra un circuito secuencial basado en el registro universal 74LS194 y en un biestable J-K con señales asíncronas de preset (PRE) y clear (CLR) activas a nivel alto. Se pide:

Figura 2.1 Circuito secuencial

a) Complete la siguiente tabla, sabiendo que la constante de tiempo del circuito de arranque es mayor que el periodo de la señal de reloj  $(\tau=R_1C_1>T_{CLK})$ . (7 ptos.)

| CLK                          | $Q_A$ | $Q_{B}$ | Q <sub>C</sub> | $Q_{\mathrm{D}}$ | J-K | $S_1$ | $S_0$ |

|------------------------------|-------|---------|----------------|------------------|-----|-------|-------|

| Conexión V <sub>CC</sub> y ↑ |       |         |                |                  |     |       |       |

| <b>1</b>                     |       |         |                |                  |     |       |       |

| 1                            |       |         |                |                  |     |       |       |

| 1                            |       |         |                |                  |     |       |       |

| <b>1</b>                     |       |         |                |                  |     |       |       |

| 1                            |       |         |                |                  |     |       |       |

| 1                            |       |         |                |                  |     |       |       |

| 1                            |       |         |                |                  |     |       |       |

| <u> </u>                     |       |         |                |                  |     |       |       |

b) Calcule, justificadamente, la máxima frecuencia de funcionamiento ( $f_{max}$ ) del circuito, a partir de los datos que se proporcionan. (3 ptos.)

**Datos:**

| Dispositivo | tiempo de<br>propagación  | tiempo de<br>setup                | tiempo de<br>hold             |

|-------------|---------------------------|-----------------------------------|-------------------------------|

| Registro:   | $t_{pR} = 36 \text{ ns}.$ | $t_{su\_s_os_i} = 15 \text{ ns.}$ | $t_{h_{-}S_{o}S_{I}}=1 \ ns.$ |

| Biestable:  | $t_{pB} = 30 \text{ ns.}$ | $t_{su} = 18 \text{ ns.}$         | $t_{h JK} = 2 ns.$            |

| Puertas:    | $t_{nP} = 10 \text{ ns}.$ |                                   |                               |

#### Cuestión 3 (10 puntos)

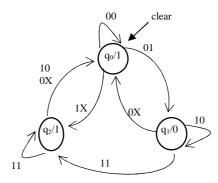

Se desea diseñar un sistema secuencial síncrono con una entrada X por donde se recibe de manera continua y en serie una cierta información. El sistema proporciona una salida Z que inicialmente es 0. Cuando en la entrada se detectan tres ceros seguidos, la salida debe tomar el valor 1, nivel en el que debe permanecer hasta que se detectan tres unos seguidos, momento en el que debe tomar el valor 0 y así sucesivamente.

Figura 3.1 Máquina de estados.

1) Realice el grafo de la máquina de estados tipo Mealy correspondiente a la aplicación descrita. (5 ptos.)

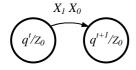

2) A partir del grafo de la figura 3.2 construya la tabla de transición de estados codificada, las funciones lógicas de excitación de los biestables tipo D y de salida, lo más simplificadas que sea posible, e implemente el circuito correspondiente. Considere las entradas clear y preset de los biestables activas a nivel bajo. (5 ptos.)

Figura 3.2

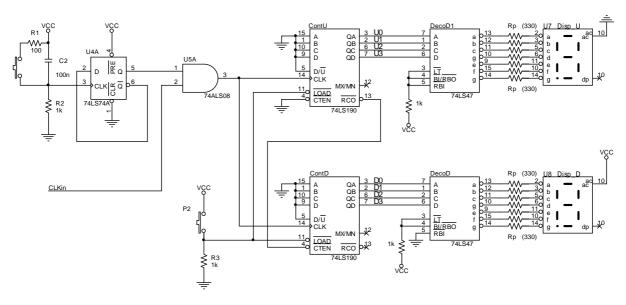

### Cuestión 4 (10 puntos)

Sobre el diseño expuesto a continuación, identifique (rodeando con un círculo) cuatro errores que impiden el funcionamiento observado en la Práctica 3. Comente, brevemente, la incidencia de cada uno de los errores en el espacio reservado. (4 ptos.)

| Error 1: |  |  |  |

|----------|--|--|--|

|          |  |  |  |

| Error 2: |  |  |  |

|          |  |  |  |

| Error 3: |  |  |  |

|          |  |  |  |

| Error 4: |  |  |  |

|          |  |  |  |

Suponiendo *solucionados los errores anteriores y, por tanto, con un funcionamiento correcto*, responda a las siguientes cuestiones. Cada pregunta tiene una única respuesta correcta que vale 2 puntos. Una respuesta errónea restará 1 punto, mientras que dejar una cuestión en blanco no penaliza.

2) ¿Cuál sería la influencia de cambiar la puerta AND por una NAND?

(2 ptos.)

- a) La señal CLKin no podrá llegar a CLK de los contadores.

- b) El contador no podrá recibir flancos de subida en su entrada CLK.

- c) El biestable D estará siempre a nivel bajo.

- d) Ninguna de las anteriores.

- 3) Teniendo en cuenta el cronograma del contador 74LS190, ¿funciona igual el diseño llevando a CTEN del contador de las decenas la salida MXMN del contador de unidades. (2 ptos.)

- a) Sí porque también es una señal de fin de cuenta.

- b) No porque se activa a nivel bajo.

- c) No porque en ese caso mientras MXMN este inactivo, el contador de decenas avanzará.

- d) Ninguna de las anteriores.

- 4) Visualizando en la pantalla del osciloscopio dos señales de salida del contador de las decenas de forma simultanea del contador de las decenas, cuál de las siguientes afirmaciones será verdadera. (2 ptos.)

- a) QB tendrá la mitad de frecuencia de QA.

- b) La señal CLK tendrá la mitad de periodo de QA.

- c) QC y QD son iguales.

- d) Ninguna de las anteriores.