## COMPUTER ARCHITECTURE

**MSI and MESI Protocols**

### □ MSI Protocol.

□ MESI Protocol.

www.uc3m.es

3

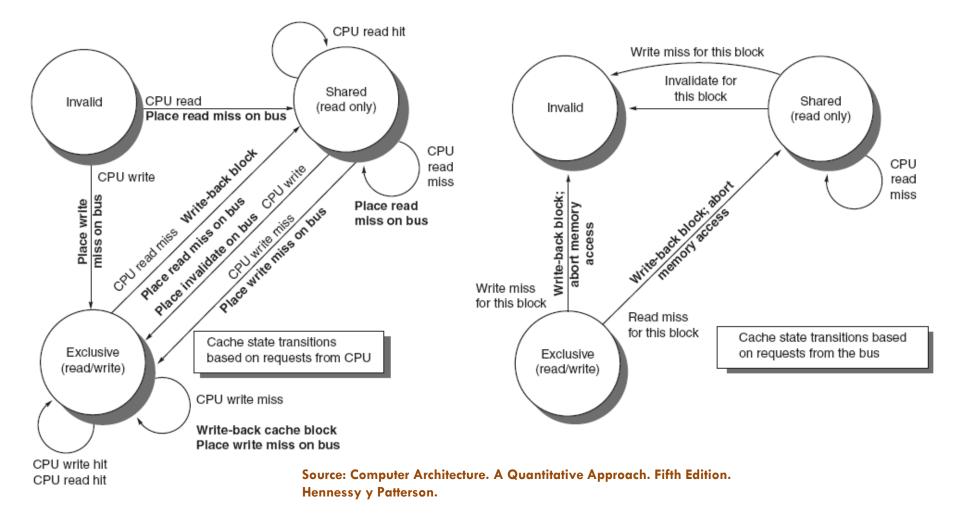

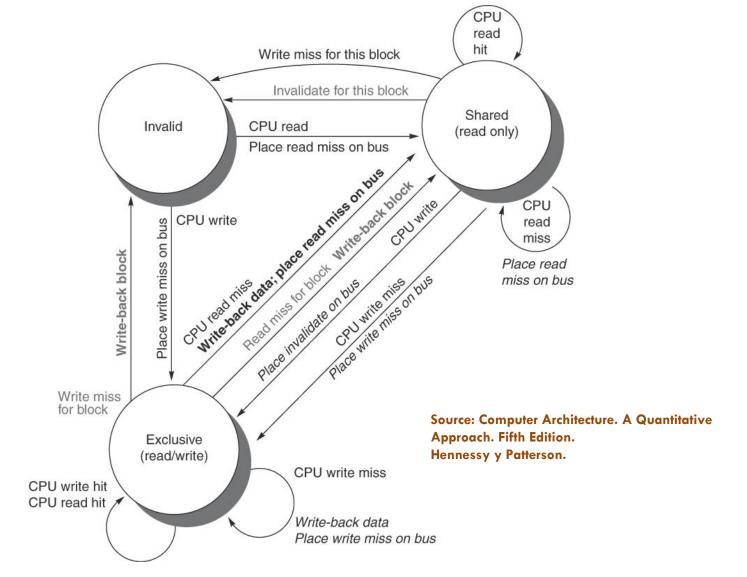

#### Universidad Carlos III de Madrid Processor generated actions protocol

| Request    | State | Action type | Description                                                          |

|------------|-------|-------------|----------------------------------------------------------------------|

| Read hit   | SoM   | Hit         | Read data in local cache.                                            |

| Read miss  | I     | Miss        | Place read miss on bus.                                              |

| Read miss  | S     | Replacement | Address conflict miss.<br>Place read miss on bus.                    |

| Read miss  | Μ     | Replacement | Address conflict miss.<br>Write back block, place read miss on bus   |

| Write hit  | Μ     | Hit         | Write data in local cache.                                           |

| Write hit  | S     | Coherence   | Place invalidate on bus.                                             |

| Write miss | I     | Miss        | Place write miss on bus.                                             |

| Write miss | S     | Replacement | Address conflict miss.<br>Place write miss on bus.                   |

| Write miss | Μ     | Replacement | Address conflict miss.<br>Write back block, place write miss on bus. |

4

www.uc3m.es

#### Bus generated actions protocol

| Request    | State | Action type | Description                                                                                           |

|------------|-------|-------------|-------------------------------------------------------------------------------------------------------|

| Read miss  | S     | -           | Shared cache or memory service miss                                                                   |

| Read miss  | Μ     | Coherence   | Attempt to share data.<br>Place cache block on bus and transition to shared.                          |

| Invalidate | S     | Coherence   | Attempt to write shared block.<br>Invalidate block.                                                   |

| Write miss | S     | Coherence   | Attempt to write shared block.<br>Invalidate block.                                                   |

| Write miss | Μ     | Coherence   | Attempt to write block that is exclusive elsewhere.<br>Write-back cache block and make state invalid. |

5

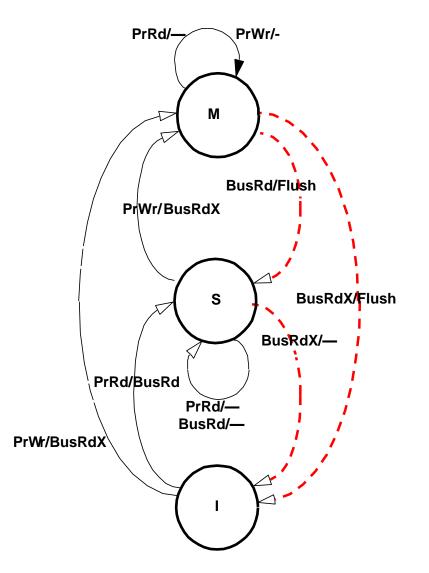

#### States:

- Invalid (I): Invalid block.

- Shared (S): One or several copies of block.

- Dirty or Modified (M): Only one copy.

#### Processor Events:

- PrRd: Processor Read.

- PrWr: Processor Write.

#### Processor Transactions:

- BusRd (read): Request a copy of block without modifying.

- BusRdX (read exclusive): Request a copy to modify.

- BusWB (write back): Update memory.

#### Actions:

Update state, perform transaction through bus and dump value to bus.

Universidad

www.uc3m.es

- Replacements and write backs not shown.

- No bus transactions due to:

- Rd/Wr in M state.

- Rd in S state.

- Two bus transactions for:

- Rd/Wr in I state.

- Wr in S state causes two bus transactions:

- Block transition to modified.

- Transition can be avoided as data is already there:

- BusUpgr instead of BusRdx

- Read and modify data are two bus transactions even if not shared.

- Even in sequential programs!

- BusRd (I->S) followed by BusRdX or BusUpgr (S->M)

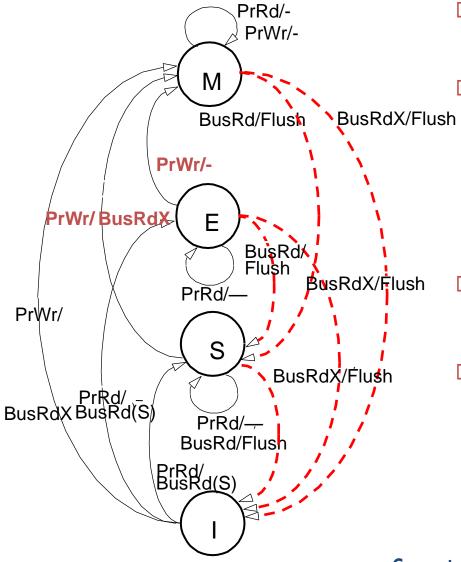

**Problems with MSI**

□ Solution:

Universidad

www.uc3m.es

Carlos III de Madrid

- Add new state: Exclusive (E).

- States:

- M: Modified (dirty).

- **E**: Exclusive (single non-modified copy).

- S: Shared.

- 🗖 l: Invalid

# MSI Protocol. MESI Protocol.

11

- Hit: No transaction in bus in E state.

- Transitions from I:

- To E with PrRd if no other processor has copy.

- To S, otherwise.

- □ S, additional signal on bus.

- BusRd(S): If processor keeps block, set S signal to 1.