## HOJA DE PROBLEMAS 9: MODULOS SECUENCIALES BÁSICOS

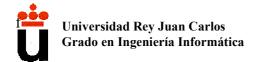

1. Diseñar un registro de 4 bits activo por flanco de subida con dos señales de control síncronas L y S, señal de puesta a 0 asíncrona (CLEAR), 5 bits de datos de entrada (ESD, X<sub>3</sub>, X<sub>2</sub>, X<sub>1</sub> y X<sub>0</sub>) y cuatro bits de salida (Q<sub>3</sub>, Q<sub>2</sub>, Q<sub>1</sub> y Q<sub>0</sub>) que realice las siguientes operaciones:

| CLEAR | Reloj      | L | S | Operación                                                 |  |  |  |

|-------|------------|---|---|-----------------------------------------------------------|--|--|--|

| 1     | X          | X | X | Puesta a 0 asíncrona                                      |  |  |  |

| 0     | $\uparrow$ | 0 | 0 | Mantenimiento del valor actual                            |  |  |  |

| 0     | $\uparrow$ | 0 | 1 | Desplazamiento hacia la derecha de longitud 1 (entra ESD) |  |  |  |

| 0     | $\uparrow$ | 1 | 0 | Carga en paralelo síncrona (entran $X_3X_2X_1X_0$ )       |  |  |  |

| 0     | $\uparrow$ | 1 | 1 | Mantenimiento del valor actual                            |  |  |  |

| 0     | Resto      | X | X | Mantenimiento del valor actual                            |  |  |  |

Se pueden utilizar en el diseño biestables de cualquier tipo con entradas síncronas y asíncronas, así como puertas lógicas y bloques estándares (multiplexores, etc.) del tamaño adecuado.

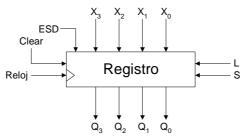

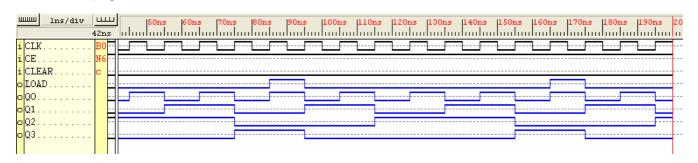

- 2. En la figura se muestra un contador estándar módulo 16 con las conexiones habituales salvo una conexión entre la señal *TC* y la señal *Load*, con un valor de entrada paralela fijo de 0101. La entrada *Clear* es asíncrona, mientras que las entradas *CE* y *Load* actúan de forma síncrona. Se pide lo siguiente:

- a) Realizar la simulación del esquema generando las formas de onda de la salida del contador (bus Q3:0) y de la salida y.

- b) ¿Qué operación está realizando el sistema?

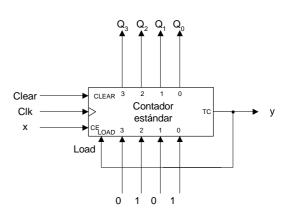

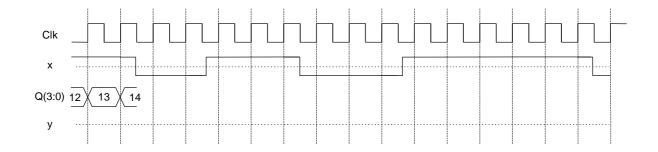

**3.** Utilizando el contador síncrono estándar módulo 16 con señal de habilitación de carga en paralelo (señal L), de la figura, se pide:

- a) Diseñar el circuito cuyo comportamiento se corresponda al cronograma de la figura inferior.

- b) ¿Qué función realiza el circuito?

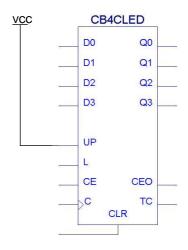

- **4.** Diseñar un contador 3-6 utilizando para ello un contador estándar del menor tamaño posible con las siguientes señales:

- UP: cuenta ascendente/descendente (UP=1, cuenta ascendente; UP=0, cuenta descendente).

- L: carga en paralelo síncrona.

- D<sub>i</sub>: entradas para carga en paralelo.

- CE: habilitación de cuenta.

- CLR: puesta a 0 asíncrona.

- Q<sub>i</sub>: contenido de los biestables del contador.

- TC, CEO: señales de fin de cuenta.

- 5. Dada una señal de reloj Clk, diseñar un divisor de frecuencia que genere una señal con una frecuencia igual a 1/3 de la frecuencia original de Clk. Utilizar para ello un contador estándar del menor tamaño posible con las señales indicadas en el enunciado del ejercicio anterior.

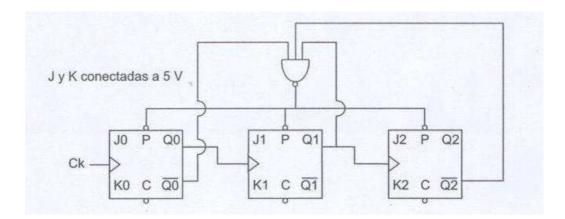

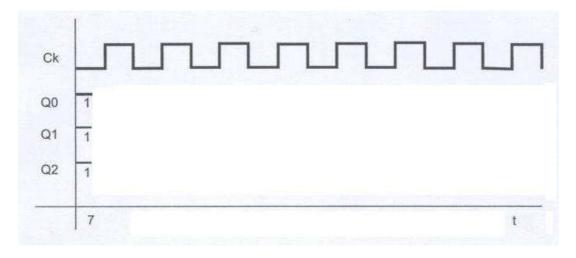

- **6.** Indicar la secuencia generada por el esquema adjunto, y completar el cronograma sin tener en cuenta los retardos. Para ello, suponer que todas las entradas J y K de los biestables están conectadas al valor lógico '1', y que la señal asíncrona de Clear está desactivada.

7. Diseñar un sistema secuencial contador modulo 8 con entrada de cuenta ascendente/descendente X={a,b} tal que si X=a realizará una cuenta ascendente y, por el contrario, si X=b realizará una cuenta descendente. Cuando la entrada cambie de X=a a X=b o viceversa el sistema continuará realizando la cuenta a partir del lugar en que se

encontraba. El sistema mostrará como salidas Z el valor de la cuenta. Se diseñará como una máquina de Moore síncrona por flanco de subida.

- a) Realizar la representación formal del sistema mediante un diagrama de estados y una tabla de estados para la máquina de Moore equivalente.

- b) Codificar los estados, las entradas y las salidas en binario.

- c) Materializar el circuito mediante las puertas lógicas y los biestables necesarios.

- **8.** Diseñar un sistema secuencial que realice una cuenta ascendente módulo 8 en código Gray. El sistema contará con una entrada de habilitación de cuenta CE, una salida de fin de cuenta TC que se activará cuando el contador llegue al valor máximo, y otra salida de fin de cuenta CEO que se activará cuando se active TC y además CE valga 1. En la materialización se emplearán biestables JK activos por flanco de subida con CLEAR asíncrono. En el diseño, seguir los pasos indicados a continuación:

- a) Especificar y explicar cuáles son los estados que ha de tener el sistema. Representar el sistema (máquina de Mealy o de Moore, como se prefiera) en forma de diagrama y tabla de estados.

- b) Realizar una asignación de estados, y escribir la tabla de transiciones y de salida del sistema

- c) Dar las expresiones de las funciones de entrada a los elementos de memoria (funciones de estado siguiente) y de salida simplificadas.

- d) Dibujar el circuito resultante.

- e) Materializar el circuito anterior con biestables de tipo D activos por flanco de subida, un único decodificador de 4 a 16 y puertas lógicas.

NOTA: La tabla siguiente muestra la representación binaria de los números del 0 al 7 en código Gray de 3 bits.

| Decimal                | 0   | 1   | 2   | 3   | 4   | 5   | 6   | 7   |

|------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Binario en código Gray | 000 | 001 | 011 | 010 | 110 | 111 | 101 | 100 |