# **Sumario**

- Introducción

- > Diseño de amplificadores operacionales

- ✓ Repaso de conceptos básicos

- ✓ Amplificadores de transconductancia (OTA) CMOS

- ✓ OTA CMOS Miller

- ✓ Asimetría, CMRR y PSSR

- > Diseño de circuitos con capacidades conmutadas

- ✓ Conceptos básicos

- ✓ Análisis

- ✓ Diseño de filtros con capacidades conmutadas

- > Estructuras analógicas programables

#### Introducción

- Revolución tecnológica en los últimos 30 años causada por las demandas del mercado y las propias necesidades tecnológicas.

- > Competencia entre implementaciones analógicas y digitales:

- ✓ enorme desarrollo de microprocesadores y DPSs

- ✓ necesidad de interfaces analógicas con el mundo real

- > Existe una tendencia creciente hacia la integración de circuitos mixtos: entornos digitales y analógicos en el mismo chip.

- > Los avances en las técnicas VLSI analógicas y digitales han cambiado la forma de particionamiento de los sistemas.

Diseño de Circuitos y Sistemas Electrónicos - Ingeniería de Telecomunicación

#### Introducción

- > En los 60 y 70, la mayor parte del diseño analógico se realizaba en tecnologías bipolares o híbridas.

- En esa época, el uso del amplificador operacional se popularizó, para pasar a ser un componente básico más en los años siguientes.

- ➤ En los 80 se desarrolló enormemente la tecnología MOS, especialmente CMOS, con el auge de los sistemas digitales.

- ➤ En los 90 se desarrolló la tecnología BiCMOS que, aunque más costosa, permite usar transistores de ambos tipos en un mismo chip.

#### Introducción

- Las aplicaciones comerciales promueven el uso de plataformas mixtas:

- ✓ comunicaciones, dispositivos multimedia, etc.

- ✓ portabilidad: alimentación por baterías, bajo consumo

- > Los circuitos mixtos analógico-digitales permiten en un solo chip:

- ✓ incluir sistemas completos (paradigma SoC: System-on-Chip)

- ✓ utilizar las características de bajo consumo y gran integración de la tecnología CMOS digital para crear sistemas de gran complejidad

- ✓ el uso de BiCMOS permite incluir en un único chip interfaces analógicas, lógica digital bipolar de gran velocidad y lógica digital CMOS de bajo consumo y gran volumen

Diseño de Circuitos y Sistemas Electrónicos - Ingeniería de Telecomunicación

#### Diseño de amplificadores operacionales

- > El amplificador operacional es uno de los bloques más versátiles y usados en aplicaciones lineales:

- √ bajo coste y elevadas prestaciones

- ✓ multitud de opciones, encapsulados, etc.

- > El amplificador operacional es un amplificador diferencial con:

- ✓ ganancia en tensión elevadísima

- ✓ impedancia de entrada muy alta

- ✓ impedancia de salida muy baja

- La realimentación permite obtener precisión en la ganancia y control del ancho de banda:

- ✓ es una necesidad en aplicaciones lineales

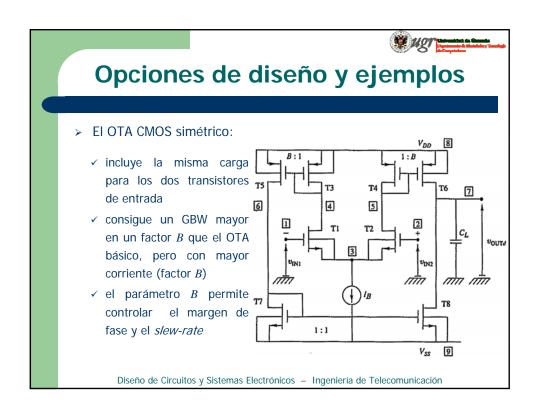

#### Diseño de amplificadores operacionales

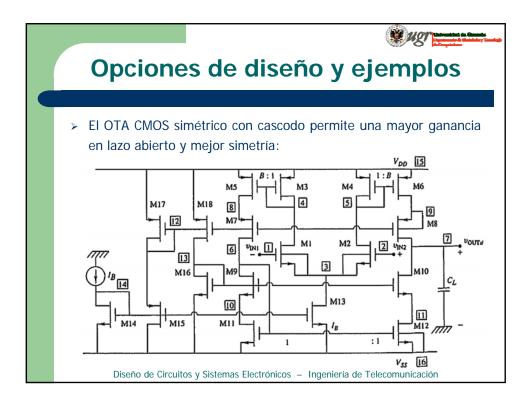

- El desarrollo de amplificadores operacionales CMOS, junto a las virtudes de la lógica CMOS, hacen de ésta una candidata ideal para circuitos mixtos.

- La necesidad de crear filtros integrados activos muy por encima de la banda de audio ha suscitado el interés en los amplificadores de transconductancia (OTA: Operational Transconductance Amplifier):

- ✓ el OTA básico consiste en una fuente de corriente controlada por tensión con una determinada ganancia de transconductancia

- > El núcleo del OTA es el amplificador diferencial, pero permite mantener el comportamiento ideal a frecuencias muy elevadas.

Diseño de Circuitos y Sistemas Electrónicos - Ingeniería de Telecomunicación

#### Amp. operacional: conceptos básicos

> Modelo básico del amplificador operacional:

- $\checkmark v_{OUT} = A_0(v^+ v^-)$

- ✓ opera como una fuente de tensión controlada por tensión

- ✓ impedancia de entrada infinita

- √ impedancia de salida nula

- ✓ v<sup>+</sup>: entrada no inversora

- √ v⁻: entrada inversora

- > Respuesta diferencial, componentes comunes canceladas.

#### Amp. operacional: conceptos básicos

> Modelo básico del amplificador operacional:

Diseño de Circuitos y Sistemas Electrónicos – Ingeniería de Telecomunicación

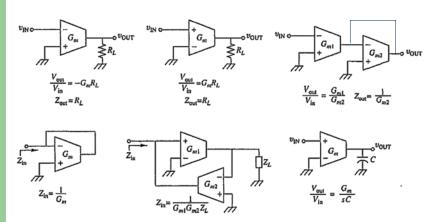

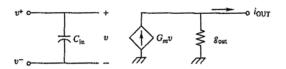

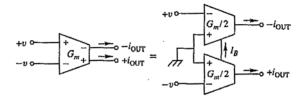

# Amplificador de transconductancia

- El amplificador de transconductancia (OTA: Operational Transconductance Amplifier) traduce entradas de tensión a salidas en corriente:

- $\checkmark$   $i_{\text{OUT}}=G_m(v^+-v^-)$

- $\checkmark G_{m}$  (ganancia de transconductancia) suele poder ajustarse con una corriente de polarización  $I_{B}$

- ✓ mucho más simples que los amplificadores operacionales estándar

- ✓ pueden mantener un comportamiento ideal a altas frecuencias

# Amplificador de transconductancia

#### Modelo ideal:

- √ impedancias de entrada y salida infinitas

- $\checkmark$  normalmente dependencia lineal entre  $G_m$  e  $I_B$ :  $G_m(I_B) = \eta I_B$

- ✓ dependencia lineal en inversión débil (MOS) o baja corriente (bipolar)

- $\checkmark$   $I_{\it B}$  puede eliminarse del símbolo ideal, aunque esto no implica que desaparezca del circuito real

- $\checkmark$   $I_B$  suele ser constante en aplicaciones lineales, pero una señal más general es muy útil para aplicaciones no lineales

Diseño de Circuitos y Sistemas Electrónicos – Ingeniería de Telecomunicación

#### ugr

# Amplificador de transconductancia

#### > Modelo ideal:

# Amplificador de transconductancia

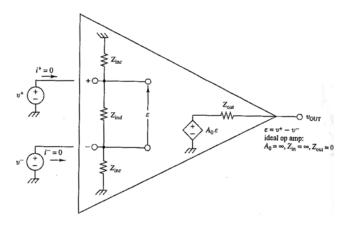

- > Limitaciones por comportamiento no ideal:

- $\checkmark$  no linealidad de  $G_m$

- $\checkmark$  variabilidad de  $G_m$  con el proceso de fabricación y la temperatura

- ✓ elementos parásitos que limitan el rango de frecuencias

- > Modelo de OTA no ideal:

Diseño de Circuitos y Sistemas Electrónicos - Ingeniería de Telecomunicación

# Amplificador de transconductancia

- Dado que los circuitos de entrada del amplificador operacional y el OTA son muy similares, ruido, offsets DC y PSRR son muy parecidos para ambos bloques.

- > El rango dinámico del OTA puede extenderse con configuraciones balanceadas:

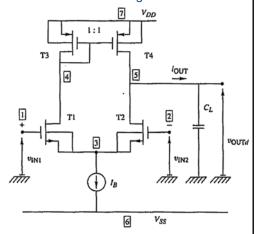

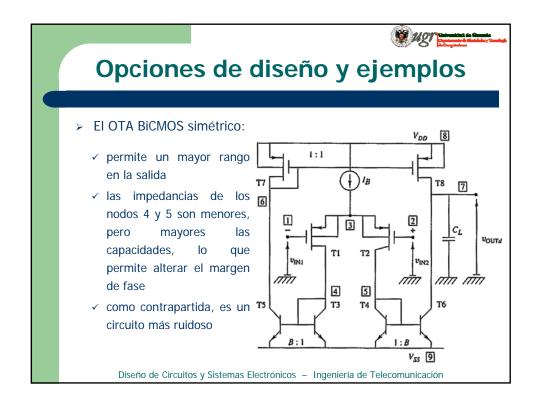

#### **OTA CMOS Básico**

- > El OTA CMOS básico corresponde a la estructura siguiente:

- ✓ Etapa diferencial nMOS con carga activa

- ✓ T1 y T2 tienen la misma relación de aspecto  $(W/L)_1$

- $\checkmark$  T3 y T4 tienen la misma relación de aspecto  $(W/L)_4$

- $\checkmark$  Nivel de corriente dado por  $I_{\scriptscriptstyle R}$

- Sustratos conectados a las fuentes para evitar efecto body

Diseño de Circuitos y Sistemas Electrónicos – Ingeniería de Telecomunicación

### **OTA CMOS Básico**

> A bajas frecuencias, la transconductancia del OTA es:

$$G_{m} = g_{m1} = g_{m2} = \sqrt{2K_{n}^{'}I_{B}\left(\frac{W}{L}\right)_{1}}$$

donde  $K'_n$  es el parámetro de transconductancia de un nMOS.

> Asumiendo  $r_{o2}$ = $r_{o4}$ , la resistencia de salida y la ganancia en tensión se pueden escribir como:

$$R_{\text{OUT}} = \frac{r_{o2}}{2} = \frac{V_{En}L_1}{I_B} \qquad A_{\text{v}} = G_{m}R_{\text{OUT}} = V_{En}\sqrt{\frac{2K_{n}^{'}W_{1}L_{1}}{I_B}} = \frac{V_{En}L_{1}}{V_{GS1} - V_{T}}$$

donde  $V_{En}$  es la tensión Early.

#### **OTA CMOS Básico**

> La resistencia entre el nodo 4 y tierra es:

$$R_{n4} = \frac{1}{g_{m3}} \left\| r_{o1} \approx \frac{1}{g_{m3}} = \frac{1}{\sqrt{2K_p^{'} I_B \left(\frac{W}{L}\right)_4}}$$

Sólo los nodos 4 y 5 causan polos, pero el polo en el nodo 5 es el dominante por su mayor resistencia (incluso sin tener en cuenta C<sub>I</sub>):

$$f_d = \frac{1}{2\pi R_{\text{OUT}} \left( C_{n5} + C_L \right)} \qquad C_{n5} = C_{GD4} + C_{DB4} + C_{GD2} + C_{DB2}$$

$$GBW = A_{v} f_{d} = \frac{g_{m1}}{2\pi \left(C_{n5} + C_{L}\right)}$$

Diseño de Circuitos y Sistemas Electrónicos – Ingeniería de Telecomunicación

### **OTA CMOS Básico**

- > La expresión general de GBW:

- $\checkmark$  está determinada por la  $g_{\it m}$  de los transistores de entrada y la capacidad dominante

- $\checkmark\,$  con un único nodo de alta resistencia,  $C_L$  es la capacidad dominante

- $\checkmark\,$  con dos nodos de alta resistencia, la capacidad Miller los conecta

- > Para una  $C_L$  dada, GBW viene determinada por  $g_{m1}$ , que puede controlarse eligiendo:

- $\checkmark$  relación de aspecto e  $I_B$

- $\checkmark \ V_{GS} V_T \ e \ I_B$

√ la elección depende del diseño

$$g_{m1} = \sqrt{2K_n'}I_B\left(\frac{W}{L}\right)_1$$

#### **OTA CMOS Básico**

> El polo no dominante se sitúa en:

$$f_{nd} = \frac{1}{2\pi R_{n4}C_{n4}} \qquad \qquad C_{n4} = C_{GD1} + C_{DB1} + C_{DB3} + C_{GS3} + \\ + C_{GS4} + C_{GD4} + C_{GB3} + C_{GB4}$$

- sólo actúa sobre la mitad de la señal (nodo 4), con lo que su efecto es el mismo de un polo a esta frecuencia y un cero al doble de la misma

- $\checkmark$  con esto, el margen de fase es:  $PM = \pi/2 \arctan \frac{GBW}{f_{nd}} + \arctan \frac{GBW}{2f_{nd}}$

- ightharpoonup Como regla, se toma como mínimo para  $f_{\it nd}$  la propia GBW; si coinciden:

$$\frac{g_{m3}}{C_{n4}} = \frac{g_{m1}}{C_{n5} + C_L} \qquad \xrightarrow{K'_n \approx 2K'_p} \qquad \left(\frac{W}{L}\right)_4 \approx 2\left(\frac{W}{L}\right)_1 \left(\frac{C_{n4}}{C_{n5} + C_L}\right)^2$$

Diseño de Circuitos y Sistemas Electrónicos – Ingeniería de Telecomunicación

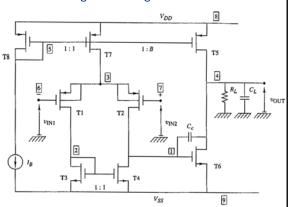

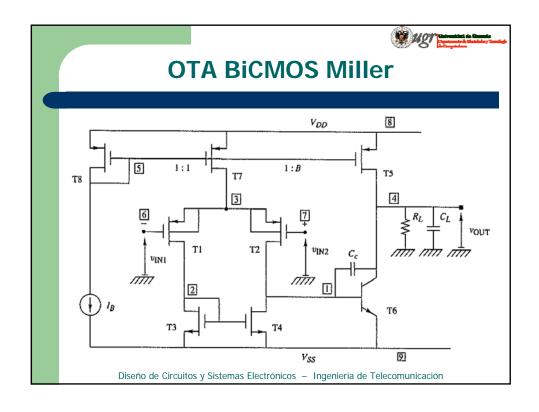

#### **OTA CMOS Miller**

- > El OTA Miller corresponde a la configuración siguiente:

- ✓ etapa diferencial pMOS con carga activa

- ✓ T5 y T6 forman un inversor CMOS, con capacidad de compensación C<sub>c</sub>

- ✓ esta capacidad actúa como la de Miller

- ✓ la configuración puede invertirse (nMOS por pMOS y viceversa)

- > Algunas consideraciones de diseño:

- ✓ no existe diferencia en el análisis de la configuración anterior o la invertida

- √ las fuentes de los transistores de entrada han de conectarse al sustrato, por lo que la configuración anterior es la adecuada para CMOS de pozo n

- ✓ la configuración invertida es adecuada para CMOS de pozo p

- $\checkmark$  T7 y T8 tienen el mismo tamaño, con lo que  $I_{\it B}$  fluye en la etapa diferencial

- √ T5 es mucho más grande, con lo que la corriente en la etapa de salida es mucho mayor

Diseño de Circuitos y Sistemas Electrónicos – Ingeniería de Telecomunicación

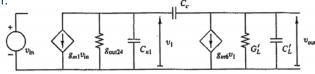

### **OTA CMOS Miller**

Para el cálculo de la ganancia utilizamos el modelo de pequeña señal:

c.

$g_{o24} = g_{o2} + g_{o4}$

$$G'_{L} = G_{L} + g_{o5} + g_{o6}$$

$$C'_L = C_L + C_{n4}$$

- > La primera etapa es un OTA y su ganancia es:  $A_{v10} = \frac{g_{m1}}{g_{v24}}$

- > La ganancia de la segunda etapa es:  $A_{v20} = \frac{g_{m6}}{G'_L}$

$$A_{\nu} = A_{\nu 10} A_{\nu 20} = \frac{g_{m1}}{g_{o24}} \frac{g_{m6}}{G'_{L}}$$

- ightharpoonup Para la respuesta a alta frecuencia se puede omitir  $C_c$  en un primer análisis:

- ✓ los nodos de entrada se suponen controlados por fuentes de baja resistencia

- ✓ el nodo común 3 puede omitirse para la ganancia diferencial

- ✓ los nodos 1, 2 y 4 determinan un sistema de tres polos, siendo la impedancia del nodo 1 la mas elevada y haciendo de éste el polo dominante:

$$f_{p1} = \frac{g_{o24}}{2\pi C_{o1}} \qquad C_{n1} = C_{GD2} + C_{DB2} + C_{GD4} + C_{DB4} + C_{GS6}$$

> Aunque este polo es de relativa baja frecuencia (kHz), está muy por encima del polo dominante de los operacionales típicos.

Diseño de Circuitos y Sistemas Electrónicos – Ingeniería de Telecomunicación

### **OTA CMOS Miller**

> Los polos no dominantes corresponden a:

$$f_{p4} = \frac{G'_{L}}{2\pi (C_{L} + C_{n4})} \qquad C_{n4} = C_{GD5} + C_{DB5} + C_{DB6}$$

$$f_{p2} = \frac{g_{m3}}{2\pi C_{n2}} \qquad C_{n2} = C_{GS3} + C_{DB3} + C_{GS4} + C_{GD4} + C_{GD4} + C_{DB1}$$

- ✓ la respuesta resultante produce un margen de fase muy pequeño, incluso negativo

- $\checkmark$  es necesario añadir  $C_c$  para corregir este efecto

ightharpoonup Incluyendo  $C_c$  tenemos un polo dominante y otro no dominante:

$$f_d \approx \frac{g_{o24}}{2\pi A_{v20} C_c}$$

$$f_{nd\,4} = \frac{g_{m6}}{2\pi C'_L} \frac{1 + \varepsilon_{GBW}}{1 + \frac{C_{n1}}{C_c} + \frac{C_{n1}}{C'_L}} \approx \frac{g_{m6}}{2\pi C'_L}$$

donde:

$$\mathcal{E}_{GBW} = \frac{G'_{L}}{g_{m6}} \left( 1 + \frac{C_{n1}}{C_{c}} \right) + \frac{g_{o24}}{g_{m6}} \left( 1 + \frac{C'_{L}}{C_{c}} \right)$$

Diseño de Circuitos y Sistemas Electrónicos – Ingeniería de Telecomunicación

wugr \_\_\_\_

### **OTA CMOS Miller**

- ightharpoonup Incluyendo  $C_c$  tenemos un polo dominante y otro no dominante:

- ✓ el ancho de banda es:

$$BW \approx f_d = f_{-3dB}$$

✓ el producto ganancia ancho de banda es:

$$GBW = \frac{g_{m1}}{2\pi C_c} \frac{1}{1 + \varepsilon_{GBW}} \approx \frac{g_{m1}}{2\pi C_c}$$

✓ el margen de fase es:

$PM = \frac{\pi}{2} - \arctan \frac{GBW}{f_{nd}}$

- > Para el análisis anterior ha de tenerse en cuenta que:

- $\checkmark$  existe también un cero en  $f_z = \frac{g_{m6}}{2\pi C_c}$  que puede ignorarse

- $\checkmark$  existe una pareja cero-polo en el nodo 2 (similar al análisis sin  $C_c$ ) que puede también ignorarse

- $\triangleright$  El efecto de  $C_c$  puede resumirse en:

- ✓ respuesta estable, incluso con ganancia unidad en realimentación

- ✓ permite mayor flexibilidad en el diseño al contar con un parámetro más

- ✓ este parámetro extra puede emplearse en reducción de área, PSRR, etc.

Diseño de Circuitos y Sistemas Electrónicos – Ingeniería de Telecomunicación

#### **OTA CMOS Miller**

- > La tensión de entrada en modo común es:  $v_{ICM} = \frac{v_{IN1} + v_{IN2}}{2}$

- ✓ limitada a tensiones que mantengan los transistores en saturación

- ✓ el límite superior se alcanza cuando T7 entra en la región lineal:

$$v_{\rm ICM\; max} = V_{\rm DD} - V_{\rm DSsat7} - V_{\rm GS1}$$

✓ en el límite inferior, los transistores de entrada han de permanecer en saturación:

$$v_{ICM\,\mathrm{min}} = V_{SS} + V_{GS3} + V_{DSsat1} - V_{GS1}$$

- ✓ el rango resultante no es simétrico, principalmente por T7

- > Si no se usa alimentación simétrica ( $V_{DD}$ = $|V_{SS}|$ ) puede desplazarse el rango para incluir  $V_{SS}$  (normalmente 0), a costa de  $v_{ICMmax}$ .

- > La tensión de salida está limitada por:

- ✓ uno de los dos transistores de salida salga de saturación, o

- ✓ la corriente sea insuficiente para la carga

- ✓ los límites resultantes son:

$$V_{OUT\,\mathrm{max}} = \min\left[V_{DD} - V_{DSsat5}, \; R_L \cdot I_{DS5}\right] \qquad \qquad V_{OUT\,\mathrm{min}} = V_{SS} + V_{DSsat6}$$

- > Los niveles máximos de corriente vienen determinados por:

- ✓ la máxima corriente que puede proporcionar T5

- ✓ la máxima corriente que puede absorber T6, que es mucho más elevada que la anterior

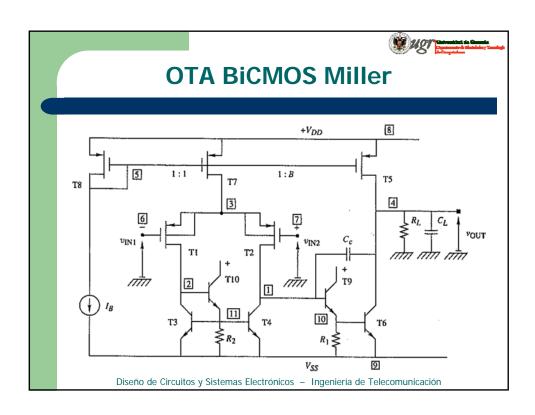

- > Reemplazar T6 por un BJT resulta en:

- mayor separación de polos, dada la mayor transconductancia del transistor bipolar

- $\checkmark$  como consecuencia, para los mismos niveles de corriente se requiere un valor menor de  $C_{c'}$  aumentando GBW

- ✓ no tiene sentido sustituir los transistores de entrada, ya que proporcionan una impedancia de entrada elevada

- > Como efectos negativos:

- $\checkmark$  la resistencia en el nodo 1 decrece  $(r_{\pi 6})$ , disminuyendo la ganancia de la primera etapa y la ganancia total

- √ se hace difícil igualar las tensiones en los nodos 1 y 2, provocando offsets

- > T6 es reemplazado por una configuración Darlington:

- ✓ su impedancia de entrada es mucho mayor, manteniendo la alta ganancia del OTA

- ✓ también se incluye un espejo de corriente de tres transistores, igualando las tensiones en los nodos 1 y 2

- > Como efectos negativos:

- ✓ se incluyen dos nuevos nodos en el circuitos, con otros dos polos no dominantes, disminuyendo el margen de fase

- $\checkmark$  la capacidad colector-sustrato de T4 incremente la capacidad en el nodo 1, aumentado el valor requerido para  $C_c$

Diseño de Circuitos y Sistemas Electrónicos – Ingeniería de Telecomunicación

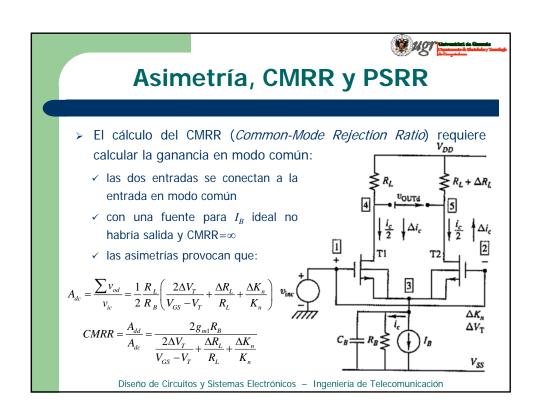

# Asimetría, CMRR y PSRR

- > La simetría y repetibilidad entre componentes (resistencias, capacidades, transistores) de un circuito integrado es uno de los factores más importantes en el diseño de sistemas analógicos:

- ✓ hasta ahora hemos supuesto componentes completamente idénticos

- √ fotolitografía, grabado, etc., provocan que componentes idénticos sean ligeramente diferentes en sus parámetros característicos

- ✓ este efecto se ve atenuado al aumentar el tamaño de los componentes

- Estas diferencias no influyen en las especificaciones principales, por lo que han de definirse otros parámetros como offsets o CMRR para cuantificar los efectos de estas asimetrías.

- Los principales parámetros de un transistor MOS que pueden verse afectados son:

- $\checkmark$   $\Delta V_T$ : las diferencias se deben a distintos grosores del óxido y dopados del sustrato, típicamente entre 10 y 25mV

- $\checkmark$   $\Delta K$ : diferencias causadas por distintos grosores del óxido y diferencias en movilidad, puede alcanzar hasta un 10%

- $\checkmark$   $\Delta \gamma$ . las diferencias se deben a distintos grosores del óxido y dopados del sustrato, puede alcanzar hasta un 5%

- √ también puede encontrarse diferencias en las resistencias

- ➤ Estas diferencias se dan entre componentes adyacentes en la misma zona de un chip (variaciones **locales**) y entre diferentes chips, diferentes obleas y diferentes tiradas (**globales**).

- Algunas simples precauciones en el diseño pueden ayudar a reducir offsets aleatorios y CMRR:

- √ sólo han de acoplarse dispositivos del mismo tipo

- dispositivos acoplados han de operar a la misma temperatura (es necesario tener en cuenta el mapa de temperatura que pueden crear dispositivos de potencia)

- ✓ aumentar el tamaño de los dispositivos acoplados

- ✓ ubicar dispositivos acoplados a la mínima distancia posible (especialmente transistores y capacidades)

- ✓ ubicar dispositivos acoplados con la misma orientación sobre el cristal

- ✓ los dispositivos acoplados han de tener la misma relación áreaperímetro

Diseño de Circuitos y Sistemas Electrónicos - Ingeniería de Telecomunicación

# Asimetría, CMRR y PSRR

- > Algunas simples precauciones en el diseño pueden ayudar a reducir *offsets* aleatorios y CMRR:

- $\checkmark$  el número de giros y esquinas han de coincidir en dispositivos acoplados

- trazar dispositivos acoplados de forma simétrica en todas direcciones, con disposición céntrica

- ✓ añadir dispositivos extra en los extremos de las series

- ✓ es preferible emplear dispositivos bipolares en lugar de MOS para elementos acoplados (sólo aplicable en tecnologías BiCMOS)

- ✓ diodos o fusibles en paralelo con secciones de resistencias pueden ayudar a corregir su valor tras la fabricación

- > En circuitos integrados en los que se mezclan funciones digitales y analógicas, ambos tipos puede interaccionar.

- > Uno de los efectos más comunes es que el reloj (o relojes) de las funciones digitales y de capacidades conmutadas, así como *buffers*/ *drivers* de salida, generen picos de corriente en:

- ✓ líneas de alimentación

- ✓ líneas de tierra

- ✓ sustrato del circuito integrado

- La inmunidad de las funciones analógicas a estas fluctuaciones se mide a través del PSSR (*Power-Supply Rejection Ratio*).

Diseño de Circuitos y Sistemas Electrónicos - Ingeniería de Telecomunicación

# Asimetría, CMRR y PSRR

- Si se reduce el consumo de los bloques analógicos, los niveles de impedancia en sus terminales aumenta, haciéndolo también la sensibilidad a señales espurias:

- ✓ al disminuir el PSRR, este efecto se ve incrementado

- Se pueden conseguir valores elevados de PSRR a bajas frecuencias, pero donde es más crítico es a altas frecuencias, donde se sitúan las fluctuaciones en la alimentación.

- ➤ El considerar la alimentación como una entrada AC más complica grandemente el cálculo de PSRR:

$$PSRR_{DD} = \frac{A_{v}}{A_{DD}} = \frac{v_{OUT} / v_{IN}}{v_{OUT} / v_{DD}} = \frac{v_{DD}}{v_{IN}}$$

$$PSRR_{SS} = \frac{A_{v}}{A_{SS}} = \frac{v_{OUT} / v_{IN}}{v_{OUT} / v_{SS}} = \frac{v_{SS}}{v_{IN}}$$

- > En los circuitos de la figura anterior:

- √ T1 y T2 se sustituyen por sus resistencias de salida, al igual que la fuente de corriente

- √ T4 se sustituye por una fuente ideal de corriente dependiente de corriente

- ✓ T3 se sustituye por  $1/g_{m3}$

- $\checkmark$  se supone que  $R_B >> r_{o24}$  y  $g_{m3} >> g_{o24}/2$

- ✓ por tanto, para frecuencias por debajo de BW:

$$A_{DD} = \frac{v_{OUT}}{v_{DD}} = \frac{1}{1 + j\frac{f}{BW}}$$

$PSRR_{DD} = \frac{A_{v}}{A_{DD}} = A_{v0}$

- > Para el análisis a frecuencias superiores:

- $\checkmark$  la magnitud de salida es la corriente a través de  $C_L$

- ✓ para frecuencias superiores a BW, esta corriente siempre es muy superior a la que fluye por  $g_{\sigma 24}$ , con lo que:

$$\frac{i_{OUT}}{v_{DD}} = g_{o24} \frac{j \frac{f}{BW}}{1 + j \frac{f}{RW}} = g_{o24} \frac{C_L s}{g_{o24} + C_L s} \qquad PSRR_{DDij} = \frac{i_{OUT} / v_{IN}}{i_{OUT} / v_{DD}} = \frac{g_{m1}}{g_{o24}}$$

✓ si se tienen en cuenta las capacidades de acoplo:

$$PSRR_{DDif} = \frac{i_{OUT} / v_{IN}}{i_{OUT} / v_{DD}} = \frac{g_{m1}}{g_{o24}} \frac{1}{1 + \frac{\left(C_{n4DD} + C_{n5DD}\right)s}{g_{o24}}}$$

Diseño de Circuitos y Sistemas Electrónicos - Ingeniería de Telecomunicación

# Asimetría, CMRR y PSRR

- $\triangleright$  Para el cálculo de PSRR<sub>SS</sub>, la influencia de  $V_{SS}$  sobre la salida se debe a dos factores:

- ✓ la corriente  $i_{SS}$  a la salida del espejo de corriente como resultado de las fluctuaciones de  $V_{SS}$  ( $v_{SS}$ )

- $\checkmark$  la corriente de salida  $i_{\mathit{OUT}}$  causada por  $i_{\mathit{SS}}$

- Si la etapa diferencial es perfectamente simétrica, i<sub>SS</sub> no produce efecto alguno en la salida (PSRR<sub>SS</sub> infinito), con lo que el posible efecto se debe a las asimetrías del circuito y PSRR<sub>SS</sub> será usualmente más elevado que PSRR<sub>DD</sub>:

$$PSRR_{SSif} = \frac{i_{OUT} / v_{IN}}{i_{OUT} / v_{DD}} = \frac{g_{m1}}{g_{o5} + C_{n3SS} s} \frac{1}{\frac{\Delta g_{m1}}{2g_{m1}} + \frac{\Delta g_{mb1}}{2g_{mb1}}}$$

# **Sumario**

- > Introducción

- > Diseño de amplificadores operacionales

- ✓ Repaso de conceptos básicos

- ✓ Amplificadores de transconductancia (OTA) CMOS

- ✓ OTA CMOS Miller

- ✓ Asimetría, CMRR y PSSR

- > Diseño de circuitos con capacidades conmutadas

- ✓ Conceptos básicos

- ✓ Análisis

- ✓ Diseño de filtros con capacidades conmutadas

- > Estructuras analógicas programables

# Capacidades conmutadas

- Los circuitos de capacidades conmutadas (SC: Switched-Capacitors) son una de las alternativas más populares para el procesamiento de señales en CMOS y BiCMOS:

- ✓ operan como un procesador de señales en tiempo discreto, pero sin necesitar convertidores A/D y D/A

- ✓ como consecuencia, puede analizarse usando la transformada z y

normalmente requieren filtro de suavizado y anti-aliasing.

- > Los bloques básicos para la creación de estos circuitos son:

- ✓ amplificadores operacionales

- ✓ capacidades

- ✓ conmutadores controlados por señales de reloj que no se solapen

Diseño de Circuitos y Sistemas Electrónicos - Ingeniería de Telecomunicación

# Capacidades conmutadas

- Una de las aplicaciones más populares es el diseño de filtros activos:

- respuesta en frecuencia muy exacta, ya que los coeficientes están determinados por relaciones entre capacidades (muy precisas en circuitos integrados)

- √ la respuesta en frecuencia es función del reloj de muestreo, que también puede fijarse de manera muy precisa

- > Además del filtrado, otras aplicaciones de los circuitos de capacidades conmutadas son:

- ✓ etapas de ganancia

- ✓ osciladores controlados por tensión

- ✓ moduladores

# Capacidades conmutadas

- > Los amplificadores incluidos en los circuitos SC han de respetar ciertas limitaciones sobre no idealidades:

- ✓ una ganancia DC baja afecta a la precisión de la función de transferencia discreta del circuito

- ✓ la frecuencia de ganancia unidad, como regla general, ha de ser al menos cinco veces superior a la frecuencia de reloj

- ✓ esto último requiere además un margen de fase de al menos 70°

- ✓ un slew-rate insuficiente puede limitar la frecuencia de reloj

- ✓ un offset DC no nulo puede traducirse en un offset DC muy elevado en la salida, dependiendo de la topología; este efecto puede reducirse con muestreo doble correlado

Diseño de Circuitos y Sistemas Electrónicos - Ingeniería de Telecomunicación

# Capacidades conmutadas

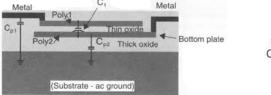

- > Las capacidades que se incluyen en estos circuitos suelen construirse a partir de dos capas de polisilicio:

- $\checkmark$  la capacidad  $C_1$  queda determinada por el área de intersección de ambas capas

- ✓ existen una capacidad parásita (hasta el 20% de la capacidad construida) debida al sustrato

- ✓ otra capacidad parásita aparece por el conexionado (hasta el 5%)

# Capacidades conmutadas

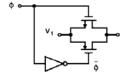

- Los conmutadores empleados en estos circuitos han de reunir ciertas características:

- ✓ resistencia en abierto muy elevada, para reducir las fugas de carga

- ✓ resistencia en conducción muy reducida

- ✓ no introducir desplazamiento de tensión en conducción

- ✓ la estructura más adecuada es la puerta de transmisión CMOS

Diseño de Circuitos y Sistemas Electrónicos - Ingeniería de Telecomunicación

# Capacidades conmutadas

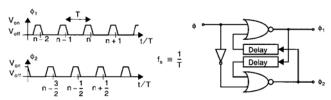

- > Un circuito SC necesita al menos dos señales de reloj que no se solapen:

- ✓ determinan cuando se producen las transferencias de carga

- √ han de no solaparse para evitar pérdidas de carga

- √ han de tener la misma frecuencia y no estar activas simultáneamente

- ✓ no es necesario un control exhaustivo de los flancos

- ✓ pueden generarse a partir de un único reloj

#### **Análisis**

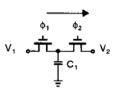

- Los circuitos de capacidades conmutadas basan su funcionamiento en la equivalencia entre una resistencia y un condensador en carga y descarga continua:

- $\checkmark$  suponiendo que  $\phi_1$  y  $\phi_2$  no se solapan,  $C_1$  se carga a  $V_1$  y  $V_2$  en cada ciclo de reloj

- en consecuencia, en cada ciclo de reloj se transfiere carga entre los dos nodos:

$$\Delta Q_1 = C_1 \left( V_1 - V_2 \right)$$

esto equivale a una corriente media que fluye entre ambos nodos:

$$I_{avg} = \frac{C_1 \left( V_1 - V_2 \right)}{T} \equiv \frac{\left( V_1 - V_2 \right)}{R_{eq}} \quad \Rightarrow \quad R_{eq} = \frac{T}{C_1} = \frac{1}{C_1 f_s}$$

Diseño de Circuitos y Sistemas Electrónicos – Ingeniería de Telecomunicación

### **Análisis**

- Los circuitos de capacidades conmutadas basan su funcionamiento en la equivalencia entre una resistencia y un condensador en carga y descarga continua:

- si se aumenta la frecuencia muestreo, con la misma cantidad de carga transferida en cada período, se incrementa la corriente media

- $\checkmark$  si se incrementa  $C_1$  aumenta la cantidad de carga transferida, aumentando la corriente media

- ✓ ambos aumentos de corriente equivalen a una disminución de la resistencia equivalente

- esta aproximación es válida a frecuencias menores que la de muestreo

#### **Análisis**

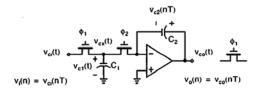

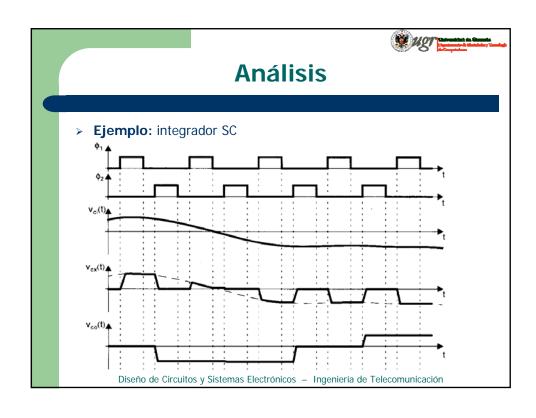

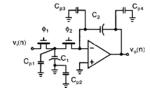

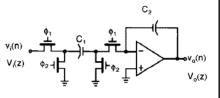

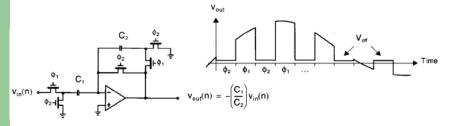

- > Ejemplo: integrador SC

- $\checkmark$  entrada y salida se muestrean con  $\phi_1$  (conmutador en la salida)

Diseño de Circuitos y Sistemas Electrónicos – Ingeniería de Telecomunicación

### **Análisis**

- > Ejemplo: integrador SC

- ✓ con  $\phi_1$  y  $\phi_2$  inactivas, la carga en las dos capacidades es en el instante nT-T:

$$Q_1 = C_1 v_{ci} \left( nT - T \right) \qquad Q_2 = C_2 v_{co} \left( nT - T \right)$$

$\checkmark$  cuando  $\phi_2$  se activa, se fuerza la descarga de  $C_1$  ( $V^-$ =0), pero la corriente resultante fluye hacia  $C_2$  y aumenta su carga, que permanece al nuevo valor mientras  $\phi_1$  está activa :

$$C_2 v_{co}(nT) = C_2 v_{co}(nT - T) - C_1 v_{ci}(nT - T)$$

$\checkmark$  usando como variables  $v_i(n)=v_{ci}(nT)$  y  $v_o(n)=v_{co}(nT)$ :

$$v_{o}(n) = v_{o}(n-1) - \frac{C_{1}}{C_{2}}v_{i}(n-1) \implies V_{o}(z) = z^{-1}V_{o}(z) - \frac{C_{1}}{C_{2}}z^{-1}V_{i}(z)$$

$$H(z) = \frac{V_{o}(z)}{V_{i}(z)} = -\frac{C_{1}}{C_{2}}\frac{z^{-1}}{1-z^{-1}} = -\frac{C_{1}}{C_{2}}\frac{1}{z-1}$$

### ugr

# **Análisis**

> Uno de los inconvenientes del circuito anterior es el efecto de las capacidades parásitas:

$$H(z) = -\frac{C_1 + C_{p1}}{C_2} \frac{1}{z - 1}$$

- ✓ el principal inconveniente es que estos parásitos no pueden controlarse adecuadamente e introducen no linealidades

- > Es posible reducir el efecto de los elementos parásitos mediante una topología adecuada del circuito.

#### **Análisis**

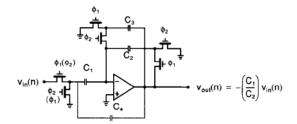

- > **Ejemplo**: integrador SC no inversor inmune a parásitos

- ✓ con  $\phi_1$  activa,  $C_1$  se carga a la tensión de entrada

- cuando φ<sub>2</sub> se activa, C<sub>1</sub> se descarga a través del nodo de tierra, aumentando la tensión de salida (para entradas positivas)

$\checkmark$  con esta configuración, las capacidades parásitas permanecen descargadas o no afectan  $(C_{p1})$  a la carga en  $C_1$

$$H(z) = \frac{V_o(z)}{V_i(z)} = \frac{C_1}{C_2} \frac{z^{-1}}{1 - z^{-1}} = \frac{C_1}{C_2} \frac{1}{z - 1}$$

Diseño de Circuitos y Sistemas Electrónicos – Ingeniería de Telecomunicación

# ugr

### **Análisis**

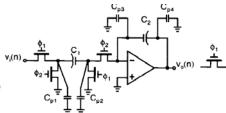

- > **Ejemplo:** integrador SC inversor inmune a parásitos

- ✓ alterando el control de los conmutadores se puede conseguir una configuración inversora

- $\checkmark$  con esta configuración, la carga en  $v_{i(2)}$   $C_2$  no se ve afectada cuando  $\phi_2$  está activa

- la función de transferencia resultante corresponde a un integrador sin retardo

$$H(z) \equiv \frac{V_o(z)}{V_i(z)} = -\frac{C_1}{C_2} \frac{z}{z-1}$$

#### **Análisis**

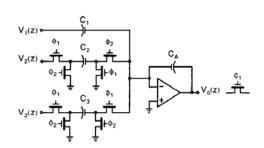

- > El análisis de los circuitos SC se puede simplificar a través de gráficos de flujo de señal:

- ✓ aplicando el principio de superposición

$$\frac{V_o(z)}{V_1(z)} = -\frac{C_1}{C_A}$$

$$\frac{V_o(z)}{V_2(z)} = \frac{C_2}{C_A} \frac{z^{-1}}{1 - z^{-1}}$$

$$\frac{V_o(z)}{V_3(z)} = -\frac{C_3}{C_A} \frac{1}{1 - z^{-1}}$$

$$V_{o}(z) = -\frac{C_{1}}{C_{A}}V_{1}(z) + \frac{C_{2}}{C_{A}}\frac{1}{1-z^{-1}}V_{2}(z) - \frac{C_{3}}{C_{A}}\frac{1}{1-z^{-1}}V_{3}(z)$$

Diseño de Circuitos y Sistemas Electrónicos – Ingeniería de Telecomunicación

### **Análisis**

> El análisis de los circuitos SC se puede simplificar a través de gráficos de flujo de señal:

$$V_{o}(z) = -\frac{C_{1}}{C_{A}}V_{1}(z) + \frac{C_{2}}{C_{A}}\frac{z^{-1}}{1 - z^{-1}}V_{2}(z) - \frac{C_{3}}{C_{A}}\frac{1}{1 - z^{-1}}V_{3}(z)$$

- este bloque representa la etapa del amplificador operacional

- ✓ las etapas de entrada se representan por tres factores según su tipo;

- o capacidad no conmutada

- o capacidad conmutada con retardo

- o capacidad conmutada sin retardo.

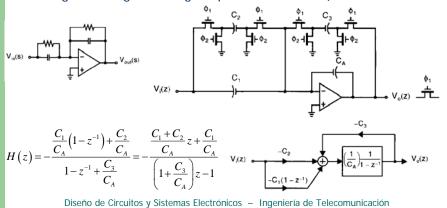

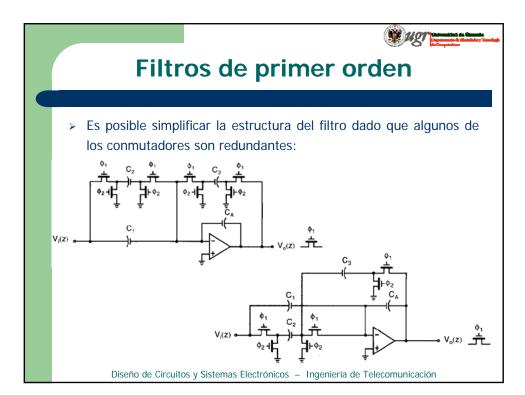

# Filtros de primer orden

- > El hecho de que a bajas frecuencias una capacidad conmutada equivale a una resistencia puede utilizarse para sustituir las resistencia en filtros activos RC:

- v puede conseguirse una resistencia de 2MΩ con una capacidad de 5pF conmutada a 100kHz, valor que requeriría un área muy elevada en un circuito integrado en el que no se empleasen pasos específicos de fabricación.

- A frecuencias más cercanas a la frecuencia del reloj, la descripción del sistema ha de hacerse en función de la transformada z.

- Las estructuras más típicas corresponden a filtros de primer orden y filtros biquad.

Diseño de Circuitos y Sistemas Electrónicos – Ingeniería de Telecomunicación

# Filtros de primer orden

> Se puede replicar la estructura del filtro RC sustituyendo las resistencias por capacidades conmutadas sin retardo (producen integración negativa, al igual que las resistencias):

33

#

# Otras aplicaciones

Offset y ruido se pueden reducir reseteando la capacidad de integración en cada ciclo de reloj:

- ✓ durante  $\phi_2$ ,  $C_1$  y  $C_2$  se cargan a la tensión de *offset* del operacional, tensión que queda cancelada en cada ciclo

- $\checkmark$  como contrapartida, la salida es sólo válida durante  $\phi_1$ , requiriendo un operacional con un muy buen <code>slew-rate</code>

Diseño de Circuitos y Sistemas Electrónicos – Ingeniería de Telecomunicación

# Otras aplicaciones

Para eliminar las restricciones de slew-rate se puede usar una configuración con reset capacitivo:

- $\checkmark$   $C_4$  mantiene la realimentación cuando los conmutadores no conducen

- ✓ al pasar de  $\phi_1$  a  $\phi_2$ , las cargas de  $C_1$  y  $C_2$  se cancelan y no afectan a  $C_3$ , con lo que la salida se mantiene independiente del *offset*

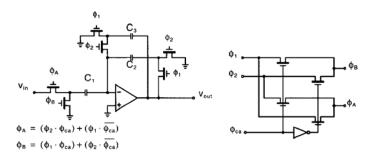

# Otras aplicaciones

> Modulador de onda cuadrada (amplitud):

- $\checkmark\,$  la polaridad de la salida se puede alterar cambiando  $\varphi_A$  por  $\varphi_B$

Diseño de Circuitos y Sistemas Electrónicos – Ingeniería de Telecomunicación

# **Sumario**

- > Introducción

- > Diseño de amplificadores operacionales

- ✓ Repaso de conceptos básicos

- ✓ Amplificadores de transconductancia (OTA) CMOS

- ✓ OTA CMOS Miller

- ✓ Asimetría, CMRR y PSSR

- > Diseño de circuitos con capacidades conmutadas

- ✓ Conceptos básicos

- ✓ Análisis

- ✓ Diseño de filtros con capacidades conmutadas

- > Estructuras analógicas programables

#### Estructuras analógicas programables

- Pese al auge de los sistemas digitales, no puede prescindirse de la electrónica analógica:

- √ acondicionamiento y preprocesamiento de señal

- ✓ interfaz entre transmisores y receptores digitales y las correspondientes antenas

- La introducción de dispositivos lógicos programables ha supuesto una gran revolución:

- √ facilidad de prototipado

- ✓ desarrollo de sistemas reprogramables con hardware dedicado

- ✓ sustitución de ASICs en aplicaciones de volumen medio o bajo

- ✓ recursos específicos para DSP, comunicaciones, etc.

Diseño de Circuitos y Sistemas Electrónicos - Ingeniería de Telecomunicación

# Estructuras analógicas programables

- Recientemente han aparecido dispositivos comerciales que tratan de extender el concepto de la lógica programable al mundo analógico:

- ✓ configuración basada en SRAM

- ✓ bloques analógicos con parámetros programables: ganancia, offset

- ✓ interfaz con sistemas digitales

- > Diferentes fabricantes están presentando diferentes alternativas:

- ✓ Anadigm: FPAA (*Field-Programmable Analog Array*) y dpASP (*dinamically programmed Analog Signal Processor*)

- ✓ Lattice: ispPAC

- ✓ Zetex: TRAC (Total Reconfigurable Analog Circuit)

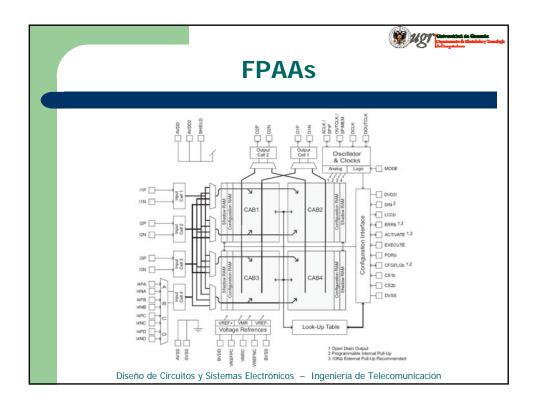

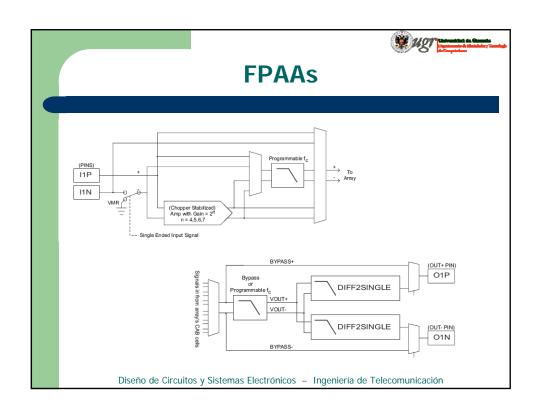

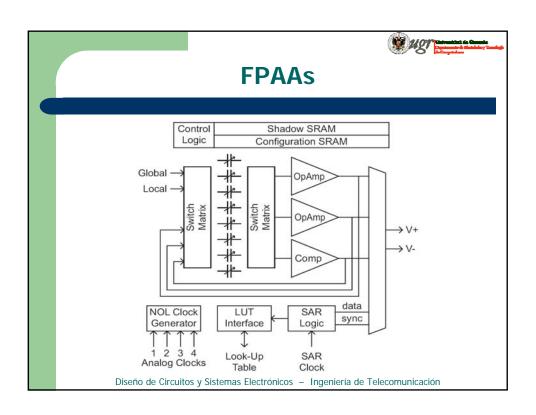

#### **FPAAs**

- > Las FPAAs son uno de los primeros dispositivos comerciales analógicos programables:

- ✓ extienden el concepto de FPGA al mundo analógico

- √ configuración basada en SRAM

- ✓ programación por ROM o microprocesador

- √ reconfiguración dinámica (125 ms)

- √ alimentación 5V (digital)

- ✓ E/S diferenciales

- ✓ LUT para linealización y generación de señales arbitrarias

- ✓ registro de aproximaciones sucesivas

- ✓ multiplexor analógico de 4 a 1

- ✓ 2MHz de ancho de banda