# Titulación: Ingeniería Informática Asignatura: Fundamentos de Computadores

**Bloque 3:** Sistemas secuenciales

Tema 7: Máquinas finitas de estados

Pablo Huerta Pellitero Luis Rincón Córcoles

## ÍNDICE

- Bibliografía

- Introducción

- Tipos de máquinas finitas de estados

- Síntesis de máquinas finitas de estados

- Síntesis de máquinas de Mealy

- Síntesis de máquinas de Moore

- Análisis de máquinas finitas de estados

- Análisis de máquinas de Mealy

- Análisis de máquinas de Moore

- Román Hermida, Ana Mº del Corral, Enric Pastor, Fermín Sánchez

"Fundamentos de Computadores", cap 3

Editorial Síntesis

- Daniel D. Gajski

"Principios de Diseño Digital", cap 5

Editorial Prentice Hall

- M. Morris Mano

"Diseño Digital", cap 4,5

Editorial Prentice Hall

### INTRODUCCIÓN

En los sistemas combinacionales la salida Z en un determinado instante de tiempo t<sub>i</sub> sólo depende de X en ese mismo instante de tiempo t<sub>i</sub>, es decir que no tienen capacidad de memoria y que se puede obviar la variable de tiempo t

$$Z(t) = F(X(t)) \Rightarrow Z = F(X)$$

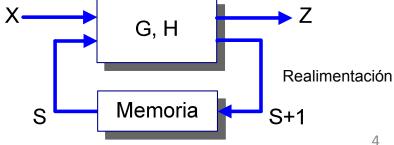

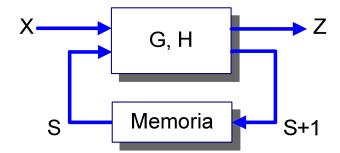

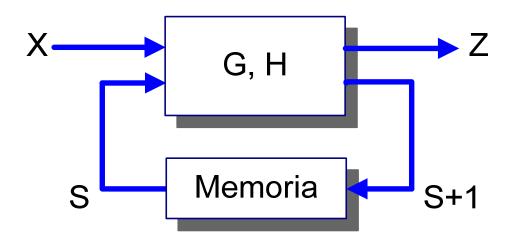

En los sistemas **secuenciales** la salida Z en un determinado instante de tiempo t<sub>i</sub> depende de X en ese mismo instante de tiempo t<sub>i</sub> y en todos los instantes temporales anteriores ¿capacidad  $\infty$  de memoria? No, todas las secuencias se resumen en un número finito de estados (FSM: máquina finita de estados)

$$Z(t) = G(X(t), S(t))$$

- Salida

$$S(t+1) = H(X(t), S(t))$$

- Cambio de estado

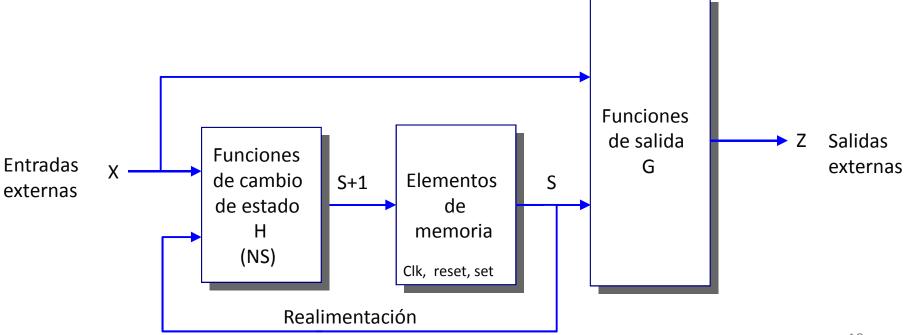

## INTRODUCCIÓN

- Un sistema secuencial dispone de **elementos de memoria** cuyo contenido puede cambiar a lo largo del tiempo. Estos elementos de memoria determinan el **estado** del sistema.

- Los sistemas secuenciales suelen tener una señal que inicia los elementos de memoria con un valor determinado: señal de inicio (reset).

- La señal de inicio determina el estado del sistema en el momento del arranque (normalmente pone toda la memoria a cero).

- La salida en un instante concreto viene dada por la entrada y por el estado del sistema.

- El estado actual del sistema, junto con la entrada, determinará el estado en el instante siguiente ⇒ realimentación.

# INTRODUCCIÓN

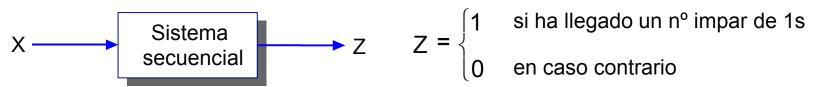

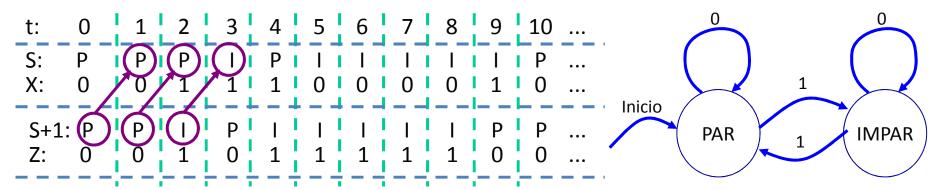

• Ejemplo: sistema secuencial que recibe datos a través de una entrada de 1 bit e indica si ha recibido un número impar de 1s.

#### Ejemplo de secuencia:

En t=0, condición inicial, hay 0 1s lo que significa un número par de 1s

En cualquier instante de tiempo **sólo hay dos posibles clases de secuencias**, las que han recibido un nº par o un nº impar de 1s, esto significa que todos los datos recibidos se pueden clasificar en dos clases o estados (S): PAR e IMPAR. Por tanto, es una Máquina Finita de Estados (FSM).

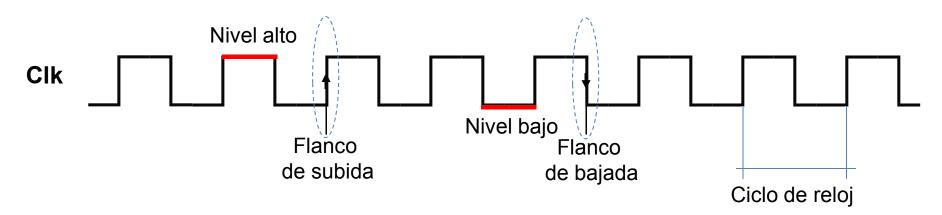

# SINCRONISMO EN MÁQUINAS DE ESTADOS

- Existen dos tipos de sistemas secuenciales: asíncronos y síncronos.

- Los asíncronos son sistemas secuenciales que pueden cambiar de estado en cualquier instante de tiempo en función de cambios en las señales de entrada.

- Los síncronos son sistemas secuenciales que sólo pueden cambiar de estado en determinados instantes de tiempos, es decir, están "sincronizados" con una señal que indica dicho instante y que se conoce como señal de reloj (Clk), sin importar si las señales de entrada han cambiado o no. Debido a su peso específico en el diseño sólo consideraremos los secuenciales síncronos.

- Bibliografía

- Introducción

- Tipos de máquinas finitas de estados

- Síntesis de máquinas finitas de estados

- Síntesis de máquinas de Mealy

- Síntesis de máquinas de Moore

- Análisis de máquinas finitas de estados

- Análisis de máquinas de Mealy

- Análisis de máquinas de Moore

# TIPOS DE MÁQUINAS FINITAS DE ESTADOS

X(t): entrada actual

Z(t): salida actual

S(t): estado actual

S(t+1): estado próximo

#### Las FSM constan de:

- Un conjunto de entradas  $X \in \{X_0, X_1, ..., X_{k-1}\}$

- Un conjunto de salidas  $Z \in \{Z_0, Z_1, ..., Z_{m-1}\}$

- Un conjunto de estados  $S \in \{S_0, S_1, ..., S_{n-1}\}$

- Una función de transición S(t+1) = H(X(t),S(t))

- Una función de salida Z(t) = G(X(t),S(t))

#### Tipos de FSM:

- Mealy

- Moore

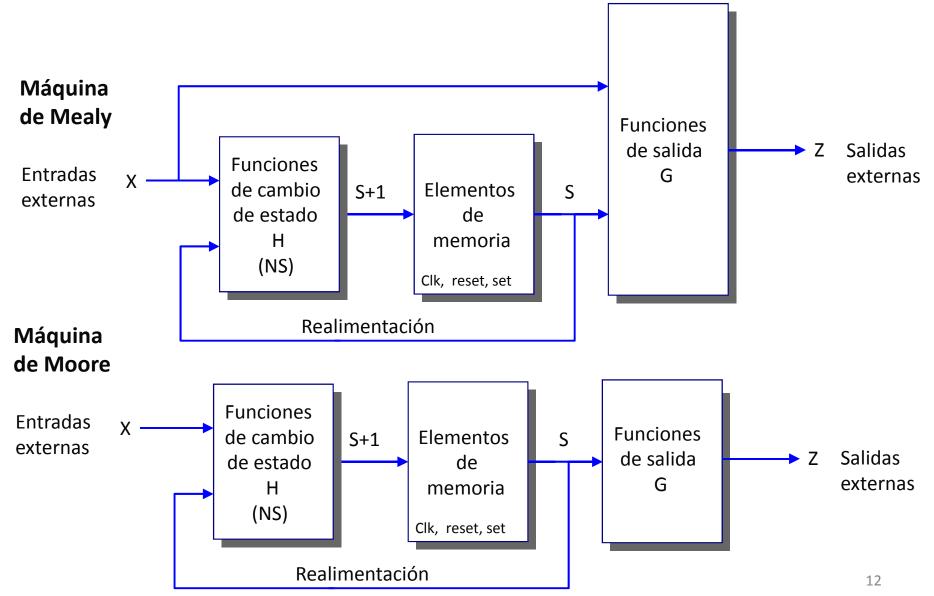

# MÁQUINAS FINITAS DE ESTADOS: MEALY

- FSM tipo Mealy:

- El próximo estado del sistema se genera a través de la función de transición de estados H que genera el próximo estado (NS), y que actúa en función del estado actual del sistema (S) y de las entradas presentes (X).

- La **función de salida** (G) se genera a partir del estado actual del sistema (S) y de los valores actuales de las entradas (X).

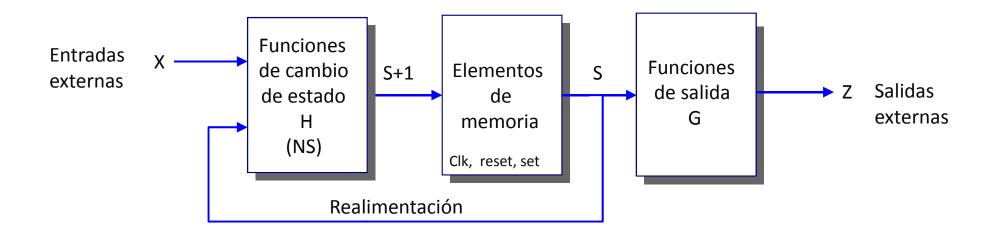

# MÁQUINAS FINITAS DE ESTADOS: MOORE

- FSM tipo Moore (caso particular de Mealy):

- El próximo estado del sistema se genera, como en las máquinas de Mealy, a través de la función de transición de estados H que genera el próximo estado (NS), y que actúa en función del estado del sistema (S) y de los valores de las entradas (X).

- La función de salida (G) se genera, a diferencia de las máquinas de Mealy, exclusivamente en función del estado actual del sistema (S), sin importar el valor de las entradas.

# MÁQUINAS FINITAS DE ESTADOS: MEALY Y MOORE

- Bibliografía

- Introducción

- Tipos de máquinas finitas de estados

- Síntesis de máquinas finitas de estados

- Síntesis de máquinas de Mealy

- Síntesis de máquinas de Moore

- Análisis de máquinas finitas de estados

- Análisis de máquinas de Mealy

- Análisis de máquinas de Moore

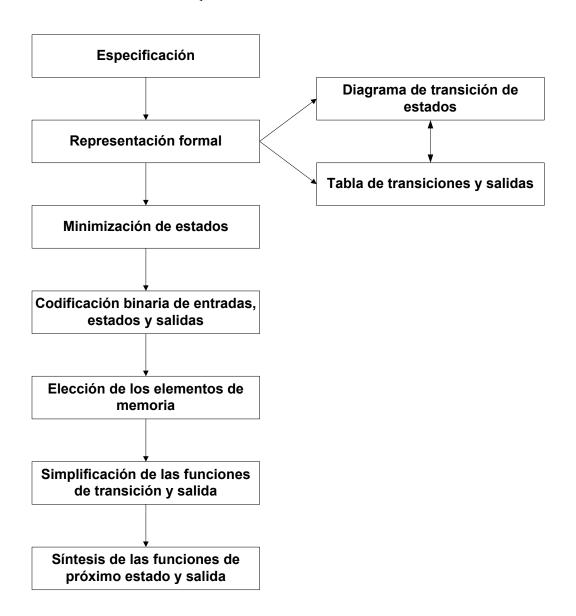

# SÍNTESIS DE MÁQUINAS FINITAS DE ESTADOS

# SÍNTESIS DE FSM: ESPECIFICACIÓN

Veremos los pasos de diseño a partir de un ejemplo.

#### Especificación de un sistema secuencial

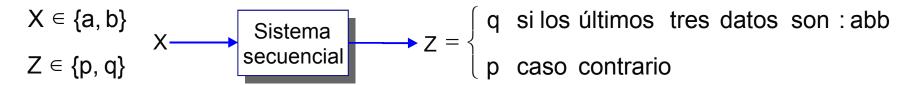

Diseñar un sistema secuencial con una entrada serie que detecte si los tres últimos datos de recibidos coinciden con la secuencia **abb**.

$$X \longrightarrow Sistema$$

$Sistema$   $Sistema$

$$Z = \begin{cases} q & \text{si los tres \'ultimos datos recibidos son abb} \\ p & \text{en caso contrario} \end{cases}$$

Después de la especificación del sistema secuencial, el siguiente paso es representarlo formalmente.

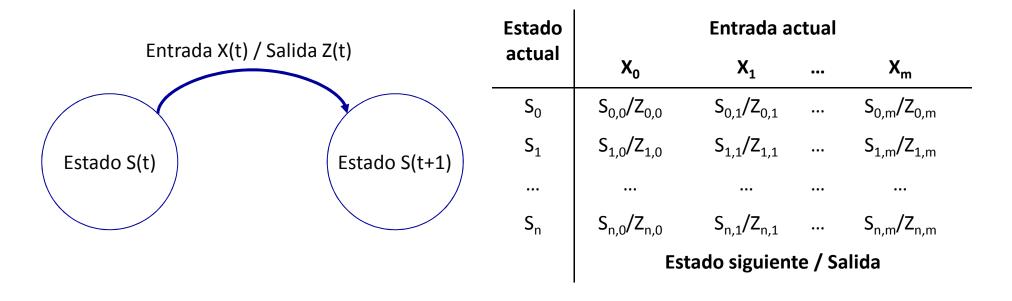

# SÍNTESIS DE FSM: REPRESENTACIÓN FORMAL - MEALY

La representación formal de un sistema secuencial se suele hacer en forma de tabla de estados y salidas o diagrama de estados. Ambas son formas equivalentes.

#### Diagrama de estados

#### Tabla de estados y salidas

# SÍNTESIS DE FSM: REPRESENTACIÓN FORMAL - MEALY

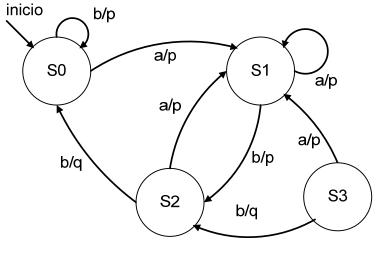

• Ejemplo: Diagrama de estados del caso propuesto.

$$Z \in \{p,q\} \qquad X \longrightarrow \begin{array}{c} \text{Sistema} \\ \text{Secuencial} \end{array} \qquad Z = \left\{ \begin{array}{c} q \text{ si los \'ultimos tres datos son : abb} \\ p \text{ caso contrario} \end{array} \right.$$

#### Diagrama de estados

#### Tabla de estados y salidas

| Estado         | Entrada actual    |                   |  |  |  |  |

|----------------|-------------------|-------------------|--|--|--|--|

| actual         | а                 | b                 |  |  |  |  |

| S <sub>0</sub> | S <sub>1</sub> /p | S <sub>0</sub> /p |  |  |  |  |

| $S_1$          | S <sub>1</sub> /p | S <sub>2</sub> /p |  |  |  |  |

| $S_2$          | S <sub>1</sub> /p | $S_0/q$           |  |  |  |  |

|                |                   | guiente /<br>lida |  |  |  |  |

# SÍNTESIS DE FSM: CODIFICACIÓN BINARIA - MEALY

- A la hora de materializar el circuito hay que transformar la tabla de estados y salidas asignando valores binarios a cada estado y salida.

- Distintas asignaciones pueden conducir a materializaciones con prestaciones distintas aunque funcionalmente equivalentes.

- Ejemplo: codificación binaria del caso propuesto.

| Entr | ada   | Sali | ida   |       | Estado | )     | Tabla de es |       |                | estados y salidas |  |  |

|------|-------|------|-------|-------|--------|-------|-------------|-------|----------------|-------------------|--|--|

| X(t) | $X_0$ | Z(t) | $Z_0$ | S(t)  | $Q_1$  | $Q_0$ | S(t)        |       | X <sub>o</sub> |                   |  |  |

| а    | 0     | р    | 0     | $S_0$ | 0      | 0     | $Q_1$       | $Q_0$ | 0              | 1                 |  |  |

| b    | 1     | q    | 1     | $S_1$ | 0      | 1     | 0           | 0     | 01/0           | 00/0              |  |  |

| •    |       | ·    |       | $S_2$ | 1      | 0     | 0           | 1     | 01/0           | 10/0              |  |  |

|      |       |      |       |       | -      |       | 1           | 0     | 01/0           | 00/1              |  |  |

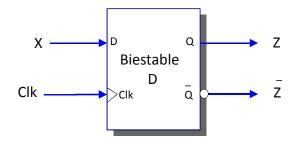

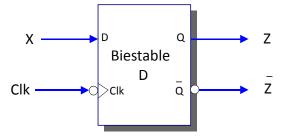

#### ELEMENTOS DE MEMORIA: BIESTABLES

- Un biestable es un dispositivo capaz de almacenar un bit (H ó L).

- El biestable siempre ofrece a la salida el valor que tiene almacenado en su interior.

- Existen diferentes tipos de biestables, pero el más adecuado y sencillo en nuestro caso es el biestable D (Delay) activo por flanco de reloj:

- El biestable D activo por flanco de subida (de bajada) captura el valor que tiene en su entrada de datos cuando se produce el flanco de subida (de bajada) del reloj.

Biestable D disparado por flanco de subida

Biestable D disparado por flanco de bajada

A los biestables activos por flanco se les denomina también flip-flops.

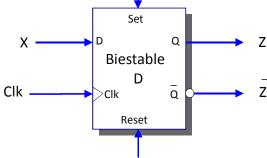

#### ELEMENTOS DE MEMORIA: BIESTABLES

Los biestables suelen tener entradas asíncronas (independientes del reloj)

que sirven para darle valor inicial:

• Reset (o Clear): puesta a 0.

Set (o Preset): puesta a 1.

- Las entradas asíncronas tienen prioridad sobre las síncronas.

- Modo de operación (biestable D activo por flanco de subida):

| Set | Reset | D | Clk          | Q(t+1) | Not Q(t+1) | _               |

|-----|-------|---|--------------|--------|------------|-----------------|

| 1   | 0     | Χ | Χ            | 1      | 0          | Set             |

| 0   | 1     | Χ | Χ            | 0      | 1          | Reset           |

| 1   | 1     | Χ | Χ            | 1      | 1          | No permitido    |

| 0   | 0     | 0 | $\uparrow$   | 0      | 1          | Flanco positivo |

| 0   | 0     | 1 | $\uparrow$   | 1      | 0          | Flanco positivo |

| 0   | 0     | Χ | 0            | Q(t)   | Not Q(t)   | Retención       |

| 0   | 0     | Χ | 1            | Q(t)   | Not Q(t)   | Retención       |

| 0   | 0     | Χ | $\downarrow$ | Q(t)   | Not Q(t)   | Retención       |

En modo síncrono, para poner un valor en un biestable D activo por flanco basta con colocar dicho valor en su entrada de datos antes de que llegue el flanco.

# SÍNTESIS DE FSM: SIMPLIFICACIÓN - MEALY

- Una vez seleccionado el tipo de biestable, la codificación binaria sirve para crear la tabla de verdad de las funciones de transición y salida (tabla de excitación y salida).

- La síntesis se realiza de forma similar a la de los circuitos combinacionales.

- Ejemplo: tabla de excitación y salida del caso propuesto.

| S     | (t)        | Х              | 0       |        |  |       | S(t), X | <b>X</b> | 9               | S(t+1), Z       |   |

|-------|------------|----------------|---------|--------|--|-------|---------|----------|-----------------|-----------------|---|

| $Q_1$ | $Q_0$      | 0              | 1       |        |  | $Q_1$ | $Q_0$   | X        | Q' <sub>1</sub> | Q' <sub>0</sub> | Z |

| 0     | 0          | 01/0           | 00/0    |        |  | 0     | 0       | 0        | 0               | 1               | 0 |

| 0     | 1          | 01/0           | 10/0    |        |  | 0     | 0       | 1        | 0               | 0               | 0 |

| 1     | 0          | 01/0           | 00/1    |        |  | 0     | 1       | 0        | 0               | 1               | 0 |

|       |            | I<br>          |         |        |  | 0     | 1       | 1        | 1               | 0               | 0 |

|       |            | Set            | 1       |        |  | 1     | 0       | 0        | 0               | 1               | 0 |

| х —   | D E        | Q<br>Biestable |         | Z      |  | 1     | 0       | 1        | 0               | 0               | 1 |

| Clk   | <b></b> >0 | D _<br>Ik Q    | <b></b> | _<br>Z |  | 1     | 1       | 0        | Х               | Χ               | Χ |

|       |            | Reset          | 1       |        |  | 1     | 1       | 1        | Х               | Χ               | X |

|       |            |                |         |        |  |       |         |          | I               |                 |   |

22

# SÍNTESIS DE FSM: SIMPLIFICACIÓN - MEALY

| :     | S(t), X | ζ | S               | s(t+1), Z                        |   | Función de transición                                                                                     |

|-------|---------|---|-----------------|----------------------------------|---|-----------------------------------------------------------------------------------------------------------|

| $Q_1$ | $Q_0$   | X | Q' <sub>1</sub> | ' <sub>1</sub> Q' <sub>0</sub> Z |   | $Q'_0(Q_1,Q_0,X_0) = \sum m(0,2,4) + \sum \Phi(6,7) \implies \frac{1}{2}$                                 |

| 0     | 0       | 0 | 0               | 1                                | 0 | $Q'_0 = D_0 = \overline{X_0}$                                                                             |

| 0     | 0       | 1 | 0               | 0                                | 0 |                                                                                                           |

| 0     | 1       | 0 | 0               | 1                                | 0 | $Q'_{1}(Q_{1},Q_{0},X_{0}) = \sum m(3) + \sum \Phi(6,7) \Rightarrow$ $Q'_{1} = D_{1} = X_{0} \cdot Q_{0}$ |

| 0     | 1       | 1 | 1               | 0                                | 0 | $\mathbf{Q}_1 = \mathbf{D}_1 = \mathbf{A}_0 \cdot \mathbf{Q}_0$                                           |

| 1     | 0       | 0 | 0               | 1                                | 0 |                                                                                                           |

| 1     | 0       | 1 | 0               | 0                                | 1 | Función de salida                                                                                         |

| 1     | 1       | 0 | Х               | Χ                                | Χ | $Z_0(Q_1,Q_0,X_0) = \sum m(5) + \sum \Phi(6,7) \implies$                                                  |

| 1     | 1       | 1 | Х               | Χ                                | X | $Z_0 = X_0 \cdot Q_1$                                                                                     |

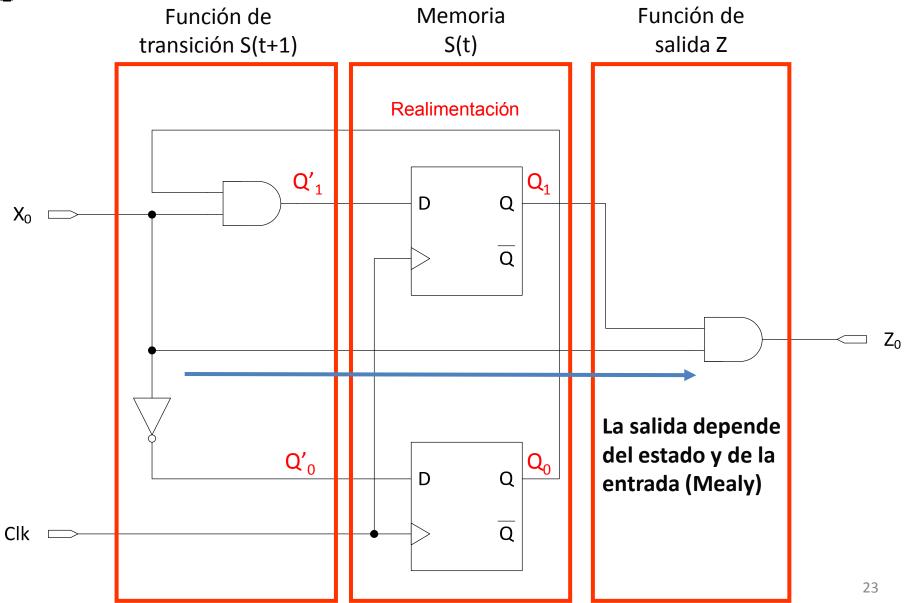

• La función de transición (par  $Q'_1-Q'_0$ ) y la función de salida ( $Z_0$ ) se materializan mediante puertas lógicas o mediante los dispositivos combinacionales que se indiquen, junto con los biestables seleccionados para almacenar el estado.

# SÍNTESIS DE FSM: MEALY

# SÍNTESIS DE FSM: REPRESENTACIÓN FORMAL - MOORE

• En la máquina de Moore, la salida no va ligada a la transición de un estado a otro, sino que depende únicamente del estado.

#### Diagrama de estados

# Estado S(t) / Salida Z(t) Estado S(t+1) / Salida Z(t+1)

#### Tabla de estados y salidas

| Estado  | Ent              |                  |     |                  |        |

|---------|------------------|------------------|-----|------------------|--------|

| actual  | $X_0$            | $X_1$            | ••• | $\mathbf{X}_{m}$ | Salida |

| $S_0$   | S <sub>0,0</sub> | S <sub>0,1</sub> |     | S <sub>0,m</sub> | $Z_0$  |

| $S_{1}$ | S <sub>1,0</sub> | S <sub>1,1</sub> | ••• | $S_{1,m}$        | $Z_1$  |

|         |                  |                  |     |                  |        |

| $S_n$   | S <sub>n,0</sub> | $S_{n,1}$        |     | $S_{n,m}$        | $Z_n$  |

|         | Esta             |                  |     |                  |        |

# SÍNTESIS DE FSM: REPRESENTACIÓN FORMAL - MOORE

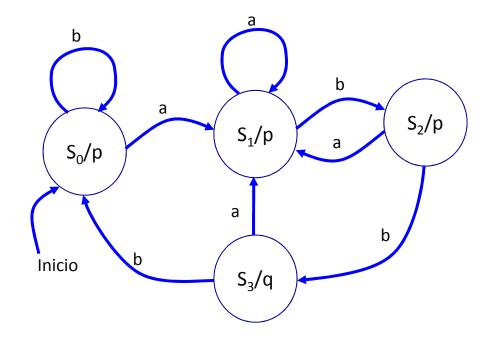

• Ejemplo: Diagrama de estados del caso propuesto.

#### Diagrama de estados

#### Tabla de estados y salidas

| Estado         | Entr           | adas         |        |

|----------------|----------------|--------------|--------|

| actual         | a b            |              | Salida |

| S <sub>0</sub> | S <sub>1</sub> | $S_0$        | р      |

| $S_1$          | $S_1$          | $S_2$        | р      |

| $S_2$          | $S_1$          | $S_3$        | р      |

| $S_3$          | $S_1$          | $S_0$        | q      |

|                |                | ado<br>iente |        |

# SÍNTESIS DE FSM: CODIFICACIÓN BINARIA - MOORE

- A la hora de materializar el circuito hay que transformar la tabla de estados y salidas asignando valores binarios a cada estado y salida.

- Distintas asignaciones pueden conducir a materializaciones con prestaciones distintas aunque funcionalmente equivalentes.

- Ejemplo: codificación binaria del caso propuesto.

| Entrada |                | _              |        |       |  |       |       | Tabla de estados |    |       |  |  |  |  |

|---------|----------------|----------------|--------|-------|--|-------|-------|------------------|----|-------|--|--|--|--|

| X(t)    | X <sub>o</sub> | i<br>I         | Estado | )     |  |       | y sa  | lidas            |    |       |  |  |  |  |

|         | 0              | S(t)           | $Q_1$  | $Q_0$ |  | S(    | t)    | X <sub>o</sub>   |    | Z     |  |  |  |  |

| b       | 1              | $S_0$          | 0      | 0     |  | $Q_1$ | $Q_0$ | 0                | 1  | $Z_0$ |  |  |  |  |

| S       | *              | $S_1$          | 0      | 1     |  | 0     | 0     | 01               | 00 | 0     |  |  |  |  |

| Sal     | ida            | S <sub>2</sub> | 1      | 0     |  | 0     | 1     | 01               | 10 | 0     |  |  |  |  |

| Z(t)    | X <sub>o</sub> | S <sub>3</sub> | 1      | 1     |  | 1     | 0     | 01               | 11 | 0     |  |  |  |  |

| р       | 0              | I              |        |       |  | 1     | 1     | 01               | 00 | 1     |  |  |  |  |

| q       | 1              |                |        |       |  |       |       | I                |    | 1     |  |  |  |  |

# SÍNTESIS DE FSM: SIMPLIFICACIÓN - MOORE

- Una vez seleccionado el tipo de biestable, crearemos las tablas de verdad de las funciones de transición y salida (tabla de excitación y tabla de salida).

- La síntesis se realiza de forma similar a la de los circuitos combinacionales.

- Ejemplo: tabla de excitación y tabla de salida del caso propuesto.

| S     | (t)       | >       | ( <sub>o</sub> | Z              |       | S(t), | ( | S(t             | +1)             |   | S(t) | ,                                                      | Z              |

|-------|-----------|---------|----------------|----------------|-------|-------|---|-----------------|-----------------|---|------|--------------------------------------------------------|----------------|

| $Q_1$ | $Q_0$     | 0       | 1              | Z <sub>o</sub> | $Q_1$ | $Q_0$ | X | Q' <sub>1</sub> | Q' <sub>0</sub> | 0 |      | $\left  \begin{array}{c} c \\ Q_0 \end{array} \right $ | Z <sub>o</sub> |

| 0     | 0         | 01      | 00             | 0              |       |       |   |                 |                 |   |      |                                                        |                |

| 0     | 1         | 01      | 10             | 0              | 0     | 0     | 0 | 0               | 1               | ( |      | 0                                                      | 0              |

| 1     | 0         | 01      | 11             | 0              | 0     | 0     | 1 | 0               | 0               | C | )    | 1                                                      | 0              |

|       |           |         |                |                | 0     | 1     | 0 | 0               | 1               | 1 | L    | 0                                                      | 0              |

| 1     | 1         | 01      | 00             | 1              | 0     | 1     | 1 | 1               | 0               | 1 | L    | 1                                                      | 1              |

|       |           | Set     |                |                | 1     | 0     | 0 | 0               | 1               |   |      | I                                                      |                |

| X —   | → D<br>Bi | estable | Q              | <b>→</b> Z     | 1     | 0     | 1 | 1               | 1               |   |      |                                                        |                |

| Clk   | CIk       | D       | ā -            | → Z̄           | 1     | 1     | 0 | 0               | 1               |   |      |                                                        |                |

|       |           | Reset   | _              |                | 1     | 1     | 1 | 0               | 0               |   |      |                                                        |                |

# SÍNTESIS DE FSM: SIMPLIFICACIÓN - MOORE

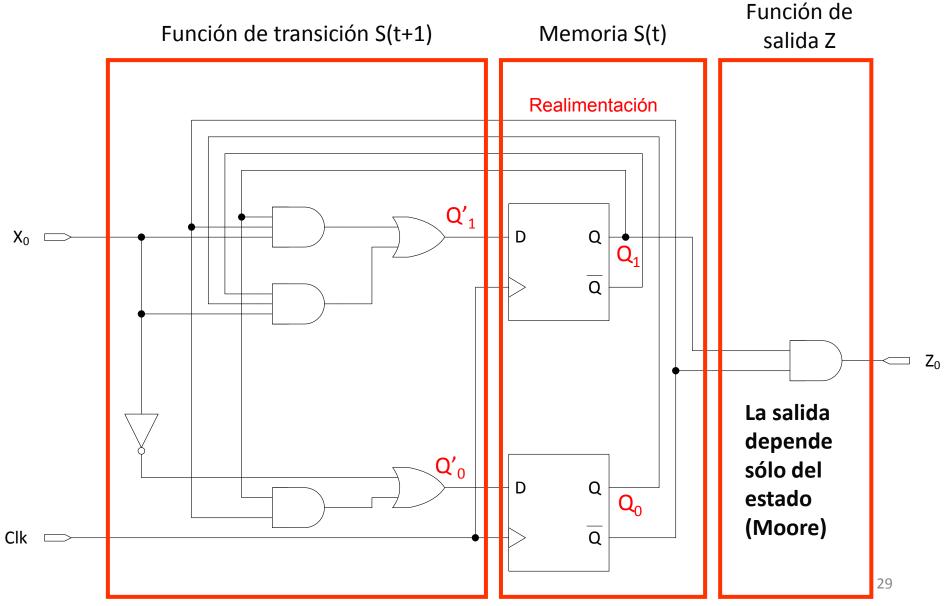

• La función de transición (par  $Q'_1-Q'_0$ ) y la función de salida ( $Z_0$ ) se materializan mediante puertas lógicas o mediante los dispositivos combinacionales que se indiquen, junto con los biestables seleccionados para almacenar el estado.

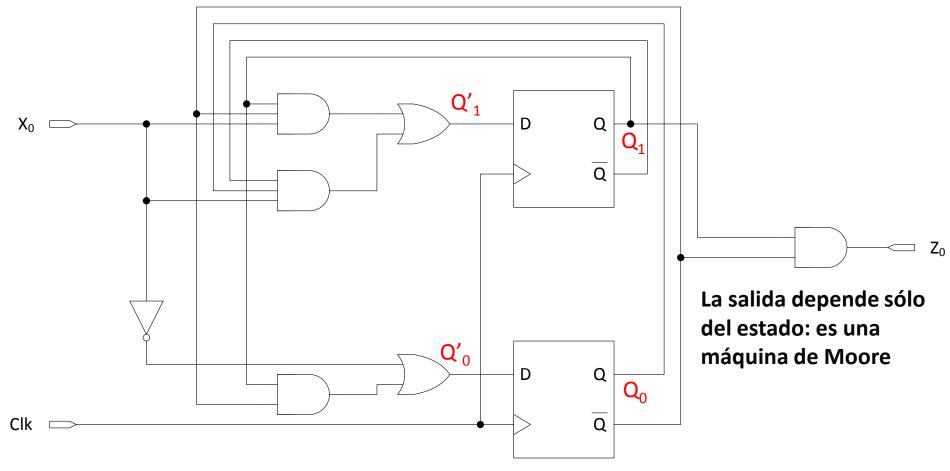

# SÍNTESIS DE FSM: MOORE

- Bibliografía

- Introducción

- Tipos de máquinas finitas de estados

- Síntesis de máquinas finitas de estados

- Síntesis de máquinas de Mealy

- Síntesis de máquinas de Moore

- Análisis de máquinas finitas de estados

- Análisis de máquinas de Mealy

- Análisis de máquinas de Moore

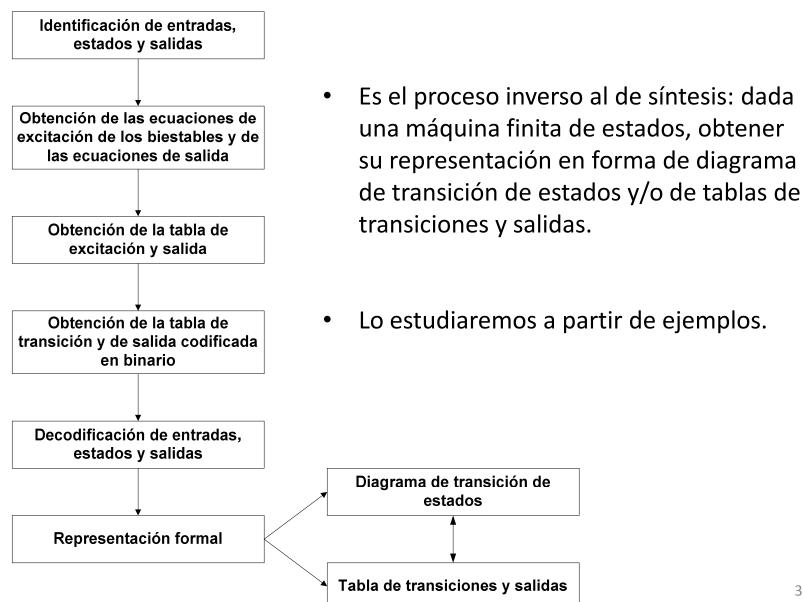

# ANÁLISIS DE MÁQUINAS FINITAS DE ESTADOS

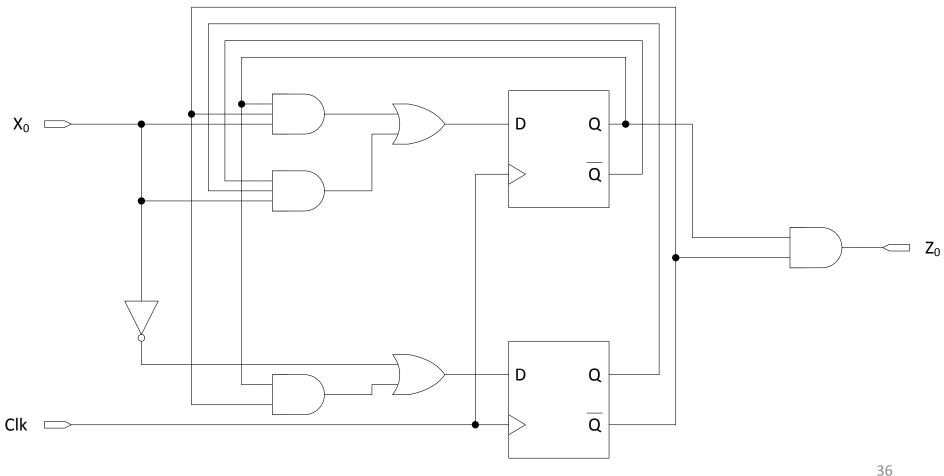

# ANÁLISIS DE FSM: EJEMPLO 1

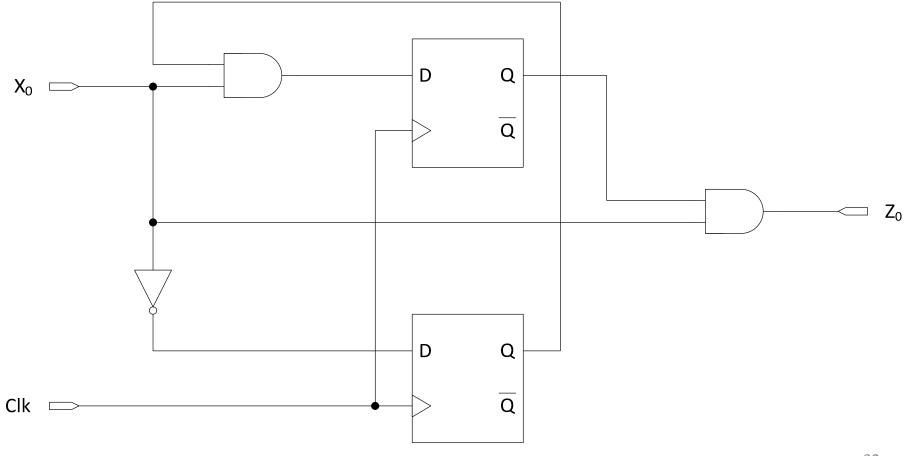

Partimos de la siguiente FSM:

# ANÁLISIS DE FSM: IDENTIFICACIÓN

• Entradas:  $X_0 \in \{0,1\}$

• Salidas:  $Z_0 \in \{0,1\}$

• Variables de estado:  $2 \{Q_1,Q_0\}$  darán lugar a 4 estados como máximo.

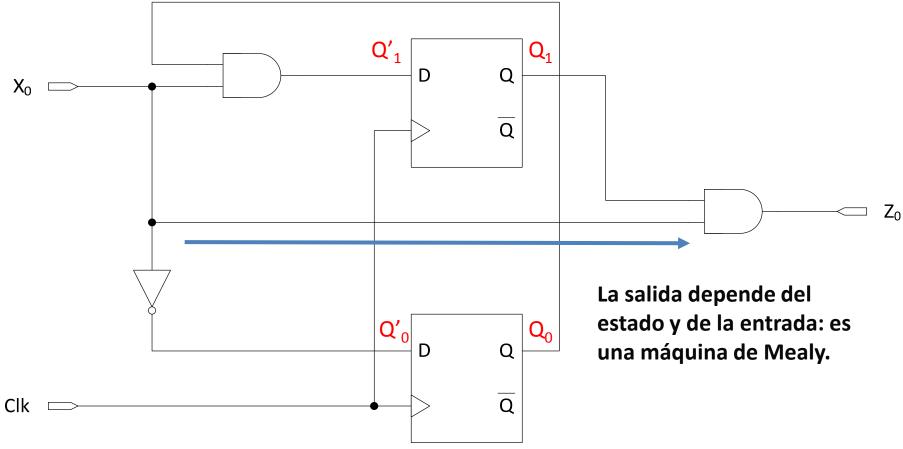

# ANÁLISIS DE FSM: ECUACIONES Y TABLAS - MEALY

#### Función de transición

$$D_0 = Q'_0 (Q_1, Q_0, X_0) = X_0$$

$D_1 = Q'_1 (Q_1, Q_0, X_0) = X_0 \cdot Q_0$

| \$    | S(t), X |   | S(t+1), Z       |        |   |  |  |  |  |

|-------|---------|---|-----------------|--------|---|--|--|--|--|

| $Q_1$ | $Q_0$   | X | Q' <sub>1</sub> | $Q_0'$ | Z |  |  |  |  |

| 0     | 0       | 0 | 0               | 1      | 0 |  |  |  |  |

| 0     | 0       | 1 | 0               | 0      | 0 |  |  |  |  |

| 0     | 1       | 0 | 0               | 1      | 0 |  |  |  |  |

| 0     | 1       | 1 | 1               | 0      | 0 |  |  |  |  |

| 1     | 0       | 0 | 0               | 1      | 0 |  |  |  |  |

| 1     | 0       | 1 | 0               | 0      | 1 |  |  |  |  |

| 1     | 1       | 0 | 0               | 1      | 0 |  |  |  |  |

| 1     | 1       | 1 | 1               | 0      | 1 |  |  |  |  |

Función de salida

$$Z_0(Q_1,Q_0,X_0) = X_0 \cdot Q_1$$

La salida depende del estado y de la entrada: es una máquina de Mealy.

| S(    | t)                          | $X_0$             |                                                                          |  |  |  |  |  |

|-------|-----------------------------|-------------------|--------------------------------------------------------------------------|--|--|--|--|--|

| $Q_1$ | $Q_0$                       | 0                 | 1                                                                        |  |  |  |  |  |

| 0     | 0                           | 01/0              | 00/0                                                                     |  |  |  |  |  |

| 0     | 1                           | 01/0              | 10/0                                                                     |  |  |  |  |  |

| 1     | 0                           | 01/0              | 00/1                                                                     |  |  |  |  |  |

| 1     | 1                           | 01/0              | 10/1                                                                     |  |  |  |  |  |

|       | <b>Q</b> <sub>1</sub> 0 0 1 | 0 0<br>0 1<br>1 0 | Q1     Q0       0     01/0       0     1     01/0       1     0     01/0 |  |  |  |  |  |

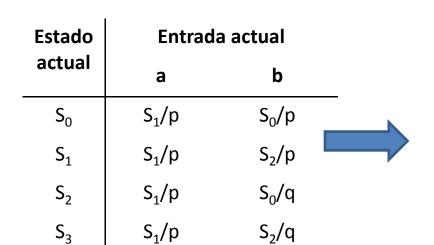

# ANÁLISIS DE FSM: DECODIFICACIÓN Y REPRESENTACIÓN FORMAL - MEALY

Asignamos nombres y valores a las entradas, los estados y la salida.

|   | S(t)  |       | х    | 0    |   | Enti  | rada |

|---|-------|-------|------|------|---|-------|------|

| - | $Q_1$ | $Q_0$ | 0    | 1    | _ | $X_0$ | X(t  |

|   | 0     | 0     | 01/0 | 00/0 | - | 0     | а    |

|   | 0     | 1     | 01/0 | 10/0 |   | 1     | b    |

|   | 1     | 0     | 01/0 | 00/1 |   |       | ı    |

|   | 1     | 1     | 01/0 | 10/1 |   |       |      |

|   |       | ļ     |      |      |   |       |      |

| Liitiaua |      |  |  |

|----------|------|--|--|

| $X_{0}$  | X(t) |  |  |

| 0        | а    |  |  |

| 1        | b    |  |  |

| Janua |      |  |  |  |

|-------|------|--|--|--|

| $Z_0$ | Z(t) |  |  |  |

| 0     | р    |  |  |  |

| 1     | q    |  |  |  |

| '     | 1    |  |  |  |

Salida

| $Q_1$ | $Q_0$ | S(t)           |

|-------|-------|----------------|

| 0     | 0     | $S_0$          |

| 0     | 1     | $S_1$          |

| 1     | 0     | S <sub>2</sub> |

| 1     | 1     | $S_3$          |

**Estado**

# ANÁLISIS DE FSM: EJEMPLO 2

Partimos de la siguiente FSM:

# ANÁLISIS DE FSM: IDENTIFICACIÓN

- Entradas:  $X_0 \in \{0,1\}$

- Salidas:  $Z_0 \in \{0,1\}$

- Variables de estado: 2 {Q<sub>1</sub>,Q<sub>0</sub>} darán lugar a 4 estados como máximo.

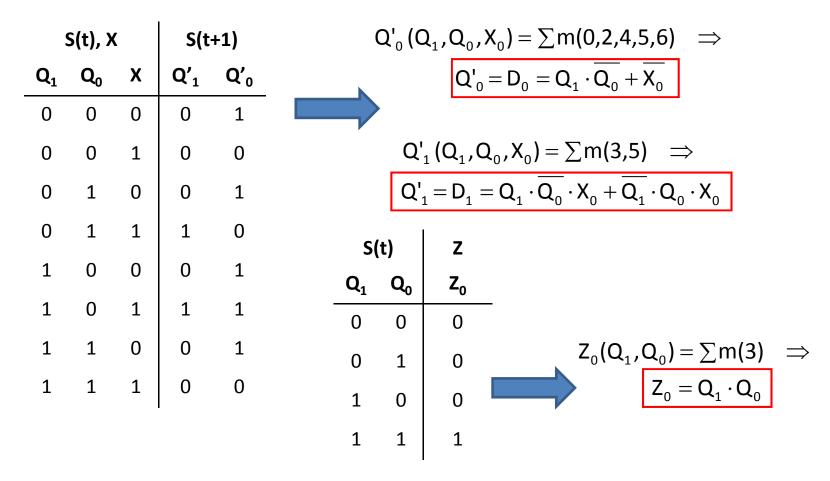

# ANÁLISIS DE FSM: ECUACIONES Y TABLAS - MOORE

$X_0$

00

10

11

00

#### Función de transición

$$D_0 = Q_0'(Q_1, Q_0, X_0) = Q_1 \cdot \overline{Q_0} + \overline{X_0}$$

$$D_1 = Q_1'(Q_1, Q_0, X_0) = Q_1 \cdot \overline{Q_0} \cdot X_0 + \overline{Q_1} \cdot Q_0 \cdot X_0$$

|    |       |       | +1)    | S(t                     |   | S(t), X | 9     |

|----|-------|-------|--------|-------------------------|---|---------|-------|

|    |       |       | $Q_0'$ | <b>Q</b> ′ <sub>1</sub> | X | $Q_0$   | $Q_1$ |

|    |       |       | 1      | 0                       | 0 | 0       | 0     |

|    | t)    | S(    | 0      | 0                       | 1 | 0       | 0     |

| 0  | $Q_0$ | $Q_1$ | 1      | 0                       | 0 | 1       | 0     |

| 02 | 0     | 0     | 0      | 1                       | 1 | 1       | 0     |

| 01 | 1     | 0     | 1      | 0                       | 0 | 0       | 1     |

| 02 | 0     | 1     | 1      | 1                       | 1 | 0       | 1     |

| 01 | 1     | 1     | 1      | 0                       | 0 | 1       | 1     |

|    |       |       | 0      | 0                       | 1 | 1       | 1     |

#### Función de salida

$$\mathsf{Z}_0(\mathsf{Q}_1,\mathsf{Q}_0) = \mathsf{Q}_1 \cdot \mathsf{Q}_0$$

La salida depende sólo del estado (Moore)

| S(    | t)    | Z     |

|-------|-------|-------|

| $Q_1$ | $Q_0$ | $Z_0$ |

| 0     | 0     | 0     |

| 0     | 1     | 0     |

| 1     | 0     | 0     |

| 1     | 1     | 1     |

# ANÁLISIS DE FSM: DECODIFICACIÓN Y REPRESENTACIÓN FORMAL - MOORF

Asignamos nombres y valores a las entradas, los estados y la salida.

| Tabla d | estac | los |

|---------|-------|-----|

|---------|-------|-----|

| S(          | (t) | Х  | <b>7</b> 0 |

|-------------|-----|----|------------|

| $Q_1$ $Q_0$ |     | 0  | 1          |

| 0           | 0   | 01 | 00         |

| 0           | 1   | 01 | 10         |

| 1           | 0   | 01 | 11         |

| 1           | 1   | 01 | 00         |

| Tabla | de | sa | lida |

|-------|----|----|------|

|       |    |    |      |

| S(t)  |                             |  |  |  |

|-------|-----------------------------|--|--|--|

| $Q_0$ | $Z_0$                       |  |  |  |

| 0     | 0                           |  |  |  |

| 1     | 0                           |  |  |  |

| 0     | 0                           |  |  |  |

| 1     | 1                           |  |  |  |

|       | <b>Q</b> <sub>0</sub> 0 1 0 |  |  |  |

#### Entrada

| $X_0$ | X(t) |

|-------|------|

| 0     | а    |

| 1     | b    |

#### Salida

| Salida |      |       | EStaut | ,              |

|--------|------|-------|--------|----------------|

| $Z_0$  | Z(t) | $Q_1$ | $Q_0$  | S(t)           |

| 0      | р    | 0     | 0      | $S_0$          |

| 1      | q    | 0     | 1      | S <sub>1</sub> |

|        | l    | 1     | 0      | S <sub>2</sub> |

|        |      | 1     | 1      | S <sub>3</sub> |

| Estado         | Entr           | adas           |

|----------------|----------------|----------------|

| actual         | а              | b              |

| $S_0$          | S <sub>1</sub> | S <sub>0</sub> |

| $S_1$          | $S_1$          | $S_2$          |

| $S_2$          | $S_1$          | $S_3$          |

| S <sub>2</sub> | S₁             | $S_{o}$        |

| Estado | Salida |

|--------|--------|

| $S_0$  | р      |

| $S_1$  | р      |

| $S_2$  | р      |

| $S_3$  | q      |

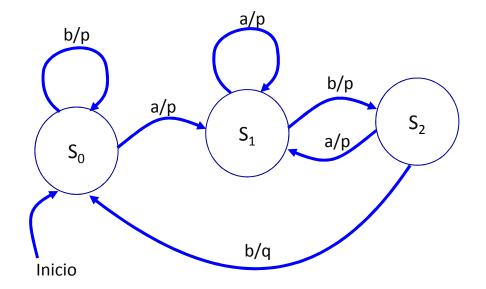

# Máquinas finitas de estado ANÁLISIS DE FSM: REPRESENTACIÓN FORMAL - MOORE

| Estado            | Entradas       |                |                 |        |                   |

|-------------------|----------------|----------------|-----------------|--------|-------------------|

| actual            | а              | b              |                 | Estado | Salida            |

| $S_0$             | S <sub>1</sub> | S <sub>0</sub> | _               | $S_0$  | р                 |

| $S_1$             | S <sub>1</sub> | $S_2$          |                 | $S_1$  | р                 |

| $S_2$             | S <sub>1</sub> | $S_3$          |                 | $S_2$  | р                 |

| $S_3$             | S <sub>1</sub> | $S_0$          |                 | $S_3$  | q                 |

| S <sub>0</sub> /I |                | a (            | $S_1/p$ $S_3/q$ | a      | S <sub>2</sub> /p |